電源電圧0.5Vで動作するミリ波帯CMOS増幅器:三重富士通セミコン DDC技術で

広島大学は2017年6月5日、三重富士通セミコンダクターの低消費電力CMOS技術「Deeply Depleted Channel(DDC)」を使用して、電源電圧0.5Vで動作するミリ波帯(W帯)増幅器を開発したと発表した。

広島大学が回路を開発

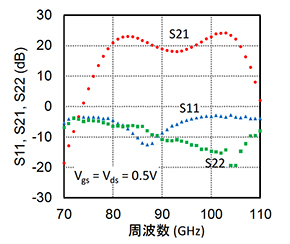

三重富士通セミコンダクター(以下、MIFS)と広島大学は2017年6月5日、MIFSの超低消費電力CMOS技術「Deeply Depleted Channel(DDC)」を使用し、80GHzから106GHzの広帯域で動作するCMOS増幅器を開発したと発表した。

DDC技術は、MIFSがスイスのCentre Suisse d'Electronique et de Microtechnique(CEMS)と共同で開発を進めているCMOS技術。トランジスタのしきい値(Vt)ばらつきを抑えて実効パフォーマンスを高められ、デバイスの電源電圧(VDD)を低減できる特長がある。MIFSでは現在、55nmCMOSプロセスで電源電圧0.5V以下を実現するDDC技術「C55DDC」の開発を実施している。なお、一般的な55nmCMOSプロセスの電源電圧は1.2V程度とされる。

従来より電源電圧を半減

今回、広島大が開発した素子特性を引き出す回路設計技術とC55DDCを組み合わせ、「CMOSとしては世界初」(MIFS/広島大)という、電源電圧0.5Vで動作する80G〜106GHz(=W帯)のミリ波帯用増幅器を実現した。MIFSと広島大では「最先端の微細プロセスに比べ耐圧の高い55nmプロセス技術を使いながら、低電圧動作させることで、消費電力の低減と信頼性の向上を達成することが可能になった」としている。

ミリ波帯増幅器は、車載レーダーシステムや第5世代移動通信(5G)基地局などで必要とされる回路。ミリ波ビームを電子的にスキャンするフェーズドアレイシステムの一部として使用されるが、同システムでは1つの送受信システムの中に数十個から数百個の送受信回路が必要になるため、増幅回路を含む送受信回路の消費電力を低減する必要性が高まっている。

広島大物質科学研究科教授の藤島実氏は「これまでW帯のCMOS増幅回路は、1.0V程度のVDDが必要だったが、今回、VDDが0.5Vでも十分な利得が得られる回路を開発できた。(MIFSの)DDC技術と組み合わせることでVDD=0.5Vでの動作を実現した」とし、従来比2分の1のVDDを達成したことで、大幅な増幅回路部分の消費電力低減が望めるとした。

なお、今回の開発成果はRF回路技術に関する国際会議「IEEE Radio Frequency Integrated Circuits Symposium 2017(RFIC 2017)」(米国ハワイ州/2017年6月4〜6日[現地時間])で発表される。

関連記事

三重富士通、IoT向け0.5V動作の55nm DDC提供へ

三重富士通、IoT向け0.5V動作の55nm DDC提供へ

三重富士通セミコンダクターは、「SEMICON Japan 2016」(2016年12月14〜16日/東京ビッグサイト)で、3つの特徴的な技術「DDC」「Plug-In Flash」「RF」について説明を行った。 独自低消費電力プロセスの40nm版、2017年量産へ

独自低消費電力プロセスの40nm版、2017年量産へ

三重富士通セミコンダクターは2015年12月16〜18日の会期で開催されている展示会「WORLD OF IOT」(併催:SEMICON Japan2015)で、独自トランジスタ構造「DDC(Deeply Depleted Channel)トランジスタ」を使用した低消費電力CMOSプロセス技術に関する展示を実施。同技術を用いた40nmプロセスによる受託量産を2017年から開始する方針を明かした。 “日本のピュアファウンドリ”に本気で挑む三重富士通の勝算

“日本のピュアファウンドリ”に本気で挑む三重富士通の勝算

富士通の半導体事業再編の中で2014年末に誕生したファウンドリ専業会社「三重富士通セミコンダクター」。台湾をはじめとした海外勢の独壇場となっている大口径の300mmウエハーによる半導体受託生産市場で、最先端微細加工技術、大きな生産能力を持たない同社はどう生き残って行くのか。同社社長の八木春良氏に聞いた。 ARMから見た7nm CMOS時代のCPU設計(11)〜回路の遅延時間を変動させるさまざまな要因

ARMから見た7nm CMOS時代のCPU設計(11)〜回路の遅延時間を変動させるさまざまな要因

今回は、回路の遅延時間を左右する要因について紹介する。例えば、コンタクト抵抗、しきい電圧、電源電圧、温度などがある。しきい電圧と温度、電源電圧と温度が遅延時間に与える影響はかなり複雑だが、その対処法として、DVFS(Dynamic Voltage and Frequency Scaling)技術が挙げられる。 FinFETの父、「半導体業界は次の100年も続く」

FinFETの父、「半導体業界は次の100年も続く」

“FinFETの父”と呼ばれる研究者のChenming Hu氏は、Synopsysのユーザー向けイベントで、「半導体業界が次の100年も続くと確信している」と述べ、業界の未来が決して暗いものではないと主張した。同氏は新しいトランジスタのアイデアとして、NC-FET(負性容量トランジスタ)についても言及した。 EUVと液浸、FinFETとFD-SOI、GFの強みは2点張り

EUVと液浸、FinFETとFD-SOI、GFの強みは2点張り

2017年5月31日、来日したGLOBALFOUNDRIES(グローバルファウンドリーズ/GF)CMOSプラットフォーム事業部シニアバイスプレジデントのGregg Bartlett氏に7nm FinFET、12nm FD-SOIの開発状況などについてインタビューした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化

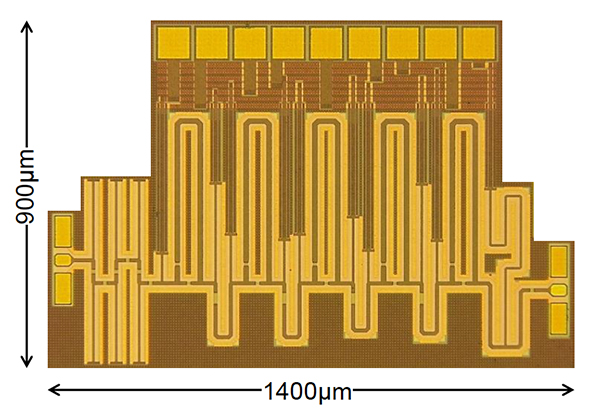

55nm DDC CMOSプロセスを用いた0.5V動作ミリ波帯(W帯)増幅回路の写真 出典:広島大学/三重富士通セミコンダクター

55nm DDC CMOSプロセスを用いた0.5V動作ミリ波帯(W帯)増幅回路の写真 出典:広島大学/三重富士通セミコンダクター