IBM、5nmナノシートで画期的成果を発表:FinFET代替なるか(1/2 ページ)

IBMなどが積層シリコンナノシートをベースにした新しいトランジスタ(シリコンナノシートトランジスタ)アーキテクチャを開発した。5nmノードの実現に向けて、FinFETに代わる技術として注目される。

FinFETと比べて消費電力を大幅に削減可能

IBMの研究チームは、パートナー企業と共に、積層シリコンナノシートをベースにした新しいトランジスタ(シリコンナノシートトランジスタ)アーキテクチャを開発したと発表した。5nmノードの実現に向けて、FinFETに代わる技術として適用できるという。

同アーキテクチャは2017年6月5日、京都で開催された半導体の回路技術に関する国際学会「2017 Symposia on VLSI Technology and Circuits」(2017年6月5〜8日)で発表された。研究アライアンスパートナーであるGLOBALFOUNDRIESとSamsung Electronics、製造装置メーカーらとの約10年にわたるナノシートの研究の末、開発に成功したという。同アーキテクチャは、FinFETと比べて消費電力を大幅に削減できるという。

シリコンナノシートトランジスタによって、スマートフォンなどのモバイル機器は1回のバッテリー充電で2〜3日間動作できるようになるという。また、性能が大きく向上することから、AI(人工知能)やVR(仮想現実)、スーパーコンピュータ(スパコン)への活用も期待できるとする。

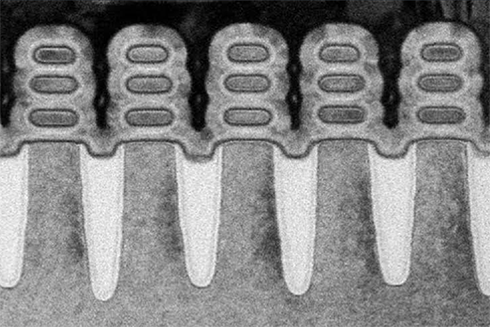

同研究アライアンスは、200億個のトランジスタを搭載した7nmプロセスのテストチップを開発してから2年もたたずして、爪の先ほどのサイズのチップに300億個のトランジスタを搭載することに成功した。同トランジスタは、ナノワイヤをゲート電極で取り囲むGAA(Gate-All-Around)構造を採用したものだ。テスト結果では、同じ電力の7nm FinFETに比べて、性能が40%向上したという。さらに、10nmプロセスのトランジスタに比べると消費電力を最大75%削減できるとした。

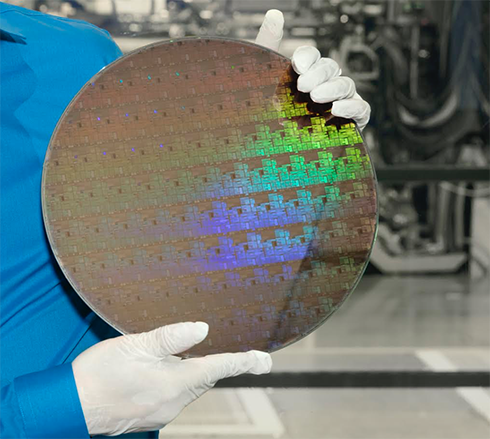

シリコンナノシートを採用したトランジスタを構築したウエハー。ウエハーを持っているのは、IBM Researchの研究員であるNicolas Loubet氏(クリックで拡大) 出典:IBM、写真:Connie Zhou氏

シリコンナノシートを採用したトランジスタを構築したウエハー。ウエハーを持っているのは、IBM Researchの研究員であるNicolas Loubet氏(クリックで拡大) 出典:IBM、写真:Connie Zhou氏IBMは、「5nmの実現に向けたこの新技術は、チップの性能を大きく向上するため、コグニティブコンピューティングや、より高いスループットを実現するクラウドコンピューティング、ディープラーニングにも貢献できると期待している。また、IoT(モノのインターネット)に必要な低消費電力、長時間バッテリー駆動という特長も備えている」と説明している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- Intelの最新AI戦略と製品 「AIが全てのタスクを引き継ぐ時代へ」

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」