FeRAMのメモリセル構造の基礎:福田昭のストレージ通信(67) 強誘電体メモリの再発見(11)(2/2 ページ)

» 2017年08月08日 10時30分 公開

[福田昭,EE Times Japan]

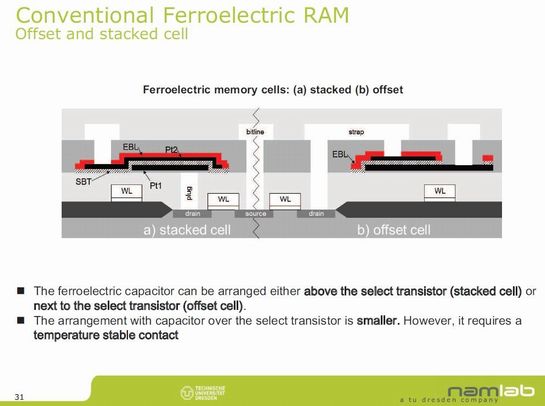

スタックセルとオフセットセル

続いてメモリセルの断面構造を考えよう。議論を容易にするため、ここでは1T1C方式だけを考える。製造工程の順番は、まずMOSFETを形成し、その後に、強誘電体キャパシターを形成する。ここで、2通りの構造が考えられる。

1つは、MOSFETのほぼ真上に強誘電体キャパシターを形成する構造である。もう1つはMOSFETの真上ではなく、位置を少しだけずらして斜め上に強誘電体キャパシターを形成する構造である。前者を「スタックセル(stacked cell)」、後者を「オフセットセル(offset cell)と呼ぶ。

メモリセルが小さくなるのは、スタックセルである。ただしこの構造ではトランジスタの拡散層とキャパシターの下部電極をプラグ金属を介して直接的に接続するため、熱的に安定なコンタクトが得られるかどうかが課題である。製造は難しくなる。

オフセットセルは、いったんトランジスタの相互接続を金属配線層に引き上げてから、キャパシターの電極に接続する。金属配線とキャパシター電極の接続になるので、安定な接続を得やすい。ただしメモリセルそのものは、大きくなる。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

主流になり得た技術、わずかな開発の遅れが命取りに

主流になり得た技術、わずかな開発の遅れが命取りに

分野によっては、技術が確立されるには、長い年月が必要になる。その一方で、わずかな開発の遅れが命取りとなり、ビジネスのチャンスを逃してしまうケースがあるのもまた、事実なのである。 磁気記憶の高密度化とその課題

磁気記憶の高密度化とその課題

磁気記憶の高密度化手法と、高密度化に伴う本質的な課題を解説する。磁気記憶は、高密度化と低消費電力化で矛盾を抱える――。 外部磁界による書き込みの限界

外部磁界による書き込みの限界

磁気トンネル接合(MTJ)を利用したデータ書き込みの原理を説明していく。まず、外部磁界による書き込みとその限界を紹介する。 IEDMで発表されていた3D XPointの基本技術(前編)

IEDMで発表されていた3D XPointの基本技術(前編)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。 WD、東芝とのメモリ合弁事業に投資継続の意思を強調

WD、東芝とのメモリ合弁事業に投資継続の意思を強調

Western Digital(ウエスタンデジタル/WD)は2017年8月2日(米国時間)、東芝とのNAND型フラッシュメモリの合弁事業に対し、今後も投資を行うとの声明を発表した。この発表の直前に東芝は、東芝メモリのメモリ新製造棟(四日市工場)への投資について協議中だったSanDisk(サンディスク:WDの子会社)と合意に至らなかったため、東芝メモリ単体で投資を続行すると発表していた。 電圧トルクMRAM、書き込みエラー率を低減

電圧トルクMRAM、書き込みエラー率を低減

産業技術総合研究所(産総研)は、電圧書込み方式磁気メモリ(電圧トルクMRAM)の書込みエラー率を従来の200分の1に低減する技術を開発した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速