Hot Chips 2017、チップ積層技術に注目集まる:IntelやXilinxも独自技術を発表(1/2 ページ)

米国カリフォルニア州クパチーノで2017年8月20〜22日に開催された「Hot Chips 2017(Host Chips 29)」では、パッケージング技術やインターコネクト技術などを含め、特に2.5D(2.5次元)のチップ積層技術に注目が集まった。

DARPAのプログラム

米国防高等研究計画局(DARPA)は、プラグアンドプレイチップレットから半導体を設計するためのエコシステムの育成を目指している。IntelやXilinxなども、独自のパッケージング技術を使用してFPGAの差別化を図っている。

DARPAの実施する「CHIPS(Common Heterogeneous Integration and IP Reuse Strategies)」プログラムは、今後8カ月で、オープンチップインタフェースについて定義し、テストを実施する計画だという。DARPAは、「複数の企業がさまざまなダイを接続して高機能チップを形成できるように、3年以内にエコシステムを構築したい」と述べている。

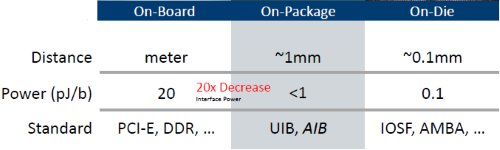

Intelは同プログラムに参加していて、他社も近く参加するとみられる。Intelは、同プログラムへの参加に伴って、同社のパッケージング技術「組み込みマルチダイインターコネクトブリッジ(EMIB)」の一部を公開するかどうかについて水面下で議論しているようだ。Intelは、米国カリフォルニア州クパチーノで2017年8月20〜22日に開催されたマイクロプロセッサの国際学会「Hot Chips」で、EMIBの最新の情報を詳細に説明した。

キャッシュコヒーレントシリアルインターコネクト(CCIX)のパイオニアであるXilinxの役員は、DARPAプログラムに関心を示している。同社は、TSMCが独自開発した2.5次元(2.5D)のパッケージング技術「CoWoS(Chip on Wafer on Substrate)」を使用した第4世代FPGAを発表した。

低コストで高帯域の接続技術が、どのようなアプローチで実現できるのかは、まだ分からない。

有機基板を使用したマルチチップモジュール(MCM)は、長年利用されてきた。同技術を、低コストで比較的密度の高い手法に改善しているベンダーもある。

TSMCは、FOWLP(Fan Out Wafer Level Packaging)技術を応用した独自のパッケージング技術「InFO」を確立し、Appleの最新の「iPhone」でアプリケーションプロセッサとメモリのパッケージングに同技術を使用した。

まだ高価な「CoWos」

AMDとNVIDIAのハイエンドGPUは、CoWoSなどの2.5D技術を使用してプロセッサとメモリスタックを接続している。ただし、「現状のままでは、民生製品には高価過ぎる」と、Microsoftのシニアエンジニアは語る。同氏は、CoWoSは高価過ぎたために、「Xbox」への搭載は見送ったという。

Microsoftと同様に、AMDは、4つのダイを搭載したサーバ向けプロセッサ「EPYC」に、高価な2.5D積層技術を採用しなかった。AMDのKevin Lepak氏は、Hot Chipsで、「MCMはよく知られている低コスト技術だが、性能面で若干のトレードオフがある。だが、EPYCにはMCMが適切だと判断した」と説明した。

DARPAプログラムが複雑な技術的障壁やビジネス上の障壁の削減につながることが、各方面から期待されている。Xilinxのシニアアーキテクトは、「チップレットがIP(Intellectual Property)化することを期待している」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

主なインターコネクト規格 出典:Intel

主なインターコネクト規格 出典:Intel