三菱電機が新型SiC-MOSFET、信頼性と省エネ両立:独自のソース領域構造で

三菱電機は、電力損失を最小レベルに抑えたSiC(炭化ケイ素)パワー半導体素子を開発した。2020年度以降の実用化を目指す。

» 2017年09月25日 09時30分 公開

[馬本隆綱,EE Times Japan]

通常は低オン抵抗、短絡発生時には電流抑制

三菱電機は2017年9月、電力損失を最小レベルに抑えたSiC(炭化ケイ素)パワー半導体素子を開発したと発表した。2020年度以降の実用化を目指す。

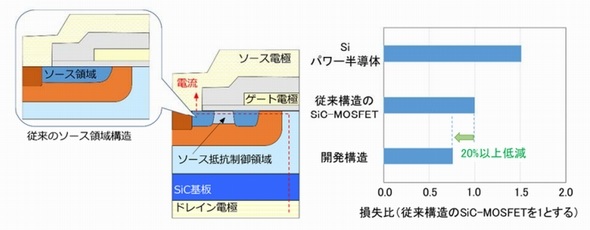

新開発のSiC-MOSFETは、ソース領域を複数に分け、ソース抵抗制御領域を形成するなど、独自の構造を採用した。これにより、使用域の温度でオン抵抗は低いが、短絡が発生すると過剰電流により温度が上昇し、抵抗が大きくなることで過剰な短絡電流が抑制され、短絡許容時間が長くなる。この結果、素子の破壊を抑制することができるという。

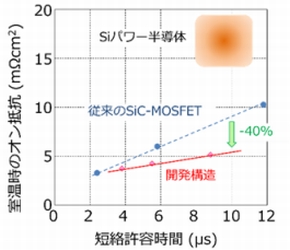

また、同一短絡許容時間で比較すると新開発のSiC-MOSFETは、ソース領域が単一構造の従来型SiC-MOSFETに比べて、室温におけるオン抵抗が約40%小さい。これにより、電力損失は20%以上も削減できるという。シリコンを用いたパワー半導体素子に比べると、オン抵抗は約60%も小さい。

パワーエレクトロニクス機器は、短絡許容時間が長いほど短絡保護回路の設計が容易となり、信頼性も向上するという。開発した素子構造はさまざまな耐圧のSiC-MOSFETに適用することが可能である。さらに、シリコンパワー半導体素子で既に用いられている短絡保護回路技術を併用すれば、より安全な保護動作を実現することができるという。

関連記事

三菱電機、未来への扉を開く研究開発戦略を発表

三菱電機、未来への扉を開く研究開発戦略を発表

三菱電機が研究開発成果の披露会を開催した。披露会では、IoTやAIを含む20点の研究開発成果を紹介すると同時に、同社の研究開発の戦略についても説明。さらに、機器やエッジへの組み込みを想定した同社独自のAIブランド「Maisart」も発表した。 三菱電機がSiC-SBDを単体で提供、高いニーズ受け

三菱電機がSiC-SBDを単体で提供、高いニーズ受け

三菱電機は「TECHNO-FRONTIER 2017(テクノフロンティア2017)」(2017年4月19〜21日、幕張メッセ)で、SiCパワーデバイスや、鉄道や大型産業機械向けの高電圧IGBTモジュール、水を流して直接冷却できる自動車用パワーモジュールなどを展示した。 三菱電機がSiC-SBDを発売、ディスクリート品は初

三菱電機がSiC-SBDを発売、ディスクリート品は初

三菱電機は、SiC(炭化ケイ素)を用いたパワー半導体の新製品「SiC-SBD」を2017年3月1日に発売した。同社はこれまでSiC-SBDやSiC-MOSFETを搭載したパワー半導体モジュールを2010年から製品化してきたが、ディスクリート品の提供は初となる。 AIで複数の同時音声を分離、再現率は驚異の90%

AIで複数の同時音声を分離、再現率は驚異の90%

三菱電機は研究成果披露会で、同社独自のAI技術「ディープクラスタリング」を用いた音声分離技術を発表した。この技術では、マイク1本で録音した複数話者の同時音声を分離し、きれいに再現できる。従来の技術では原音再現率が51%だったが、三菱電機の音声分離技術の場合90%以上となる。 HEV用SiCインバーター、体積は「世界最小」

HEV用SiCインバーター、体積は「世界最小」

三菱電機は、体積が5リットルと小さいHEV用「SiC(炭化ケイ素)インバーター」を開発した。 短絡電流を13ミリ秒以内に遮断する技術、鉄道向け

短絡電流を13ミリ秒以内に遮断する技術、鉄道向け

三菱電機は2017年1月、鉄道向け電力供給システムを保護する直流遮断器において、異常時に発生する短絡電流を検出し、「世界最速」とする13ミリ秒以内に遮断する技術を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

左は開発したSiC-MOSFETの断面構造図、右は従来品と損失低減効果を比較したグラフ 出典:三菱電機

左は開発したSiC-MOSFETの断面構造図、右は従来品と損失低減効果を比較したグラフ 出典:三菱電機 室温におけるオン抵抗と短絡許容時間の関係を示すグラフ 出典:三菱電機

室温におけるオン抵抗と短絡許容時間の関係を示すグラフ 出典:三菱電機