ISSCC技術講演の2日目午後ハイライト(その1)、深層学習の高速実行エンジンと超低消費電力のA-D変換器チップ:福田昭のデバイス通信(130) 2月開催予定のISSCC 2018をプレビュー(6)(2/2 ページ)

» 2018年01月11日 10時30分 公開

[福田昭,EE Times Japan]

有効ビット数が15ビットで消費電力が4.5μWと極めて小さなA-D変換器チップ

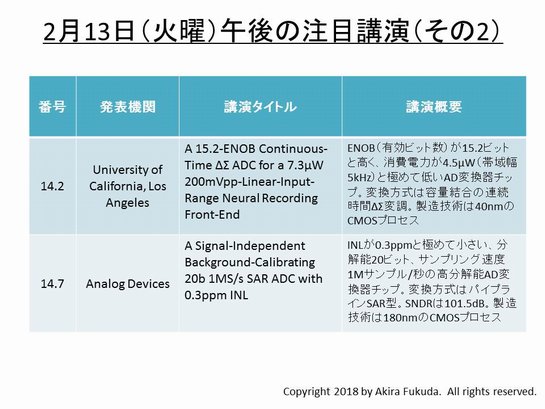

セッション14の「高分解能のアナログデジタル変換(A-D変換)器」では、超低消費電力のAD変換器と超高分解能のA-D変換器が登場する。

UCLA(University of California, Los Angeles)は、有効ビット数(ENOB: Effective Number Of Bits)が15.2ビットと高く、消費電力が4.5μW(帯域幅は5kHz)と極めて低いAD変換器チップを開発した(講演番号14.2)。生体神経の信号計測用である。変換方式は容量結合の連続時間ΔΣ(デルタシグマ)変調方式。製造技術は40nmのCMOSプロセスである。

Analog Devicesは、積分非直線性誤差(INL: Integral Non Linearity)が0.3ppmと極めて小さく、分解能が20ビットと高いAD変換器チップを発表する(講演番号14.7)。変換方式はパイプラインSAR(Successive Approximation Register)型。サンプリング速度は1Mサンプル/秒である。バックグラウンドでキャリブレーションを実行することで歪みを低く抑えた。SNDR(Signal-to-Noise and Distortion Ratio)は101.5dB。製造技術は180nmのCMOSプロセスである。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ISSCC技術講演の2日目午前ハイライト(その1)、強化学習する超小型ロボット、Wi-Fi電波からエネルギーを収穫する回路など

ISSCC技術講演の2日目午前ハイライト(その1)、強化学習する超小型ロボット、Wi-Fi電波からエネルギーを収穫する回路など

「ISSCC 2018」2日目午前から、注目講演を紹介する。低ジッタのクロック回路技術や、2.4GHz帯のWi-Fi電波からエネルギーを収穫する環境発電回路などについての講演が発表される。 Intelの高性能・高密度パッケージング技術「EMIB」の概要

Intelの高性能・高密度パッケージング技術「EMIB」の概要

今回は、Intelが開発した2.nD(2.n次元)のパッケージング技術「EMIB(Embedded Multi-die Interconnect Bridge)」を解説する。EMIBではシリコンインターポーザの代わりに「シリコンブリッジ」を使う。その利点とは何だろうか。 Samsung、10nmクラスの8Gb DDR4 DRAMを量産開始

Samsung、10nmクラスの8Gb DDR4 DRAMを量産開始

Samsung Electronicsが、10nmクラスのプロセスを採用した第2世代の8GビットDDR4 DRAMの量産を開始したと発表した。 「不揮発性DRAM」へのアプローチ(前編)

「不揮発性DRAM」へのアプローチ(前編)

今回から、「不揮発性DRAM」の実現を目指す研究開発について解説する。二酸化ジルコニウムは、その結晶構造から、工夫次第で強誘電体のような不揮発性を付加できる可能性がある。 組み込みに特化した商用の深層学習フレームワーク

組み込みに特化した商用の深層学習フレームワーク

ディープインサイトは、「Embedded Technology 2017(ET2017)/IoT Technology 2017」で、組み込み機器に特化した商用の深層学習フレームワークを使い、CPUで高速に推論処理を実行するデモを行った。 深層学習のコアライブラリー、ソニーが無償公開

深層学習のコアライブラリー、ソニーが無償公開

ソニーは、ディープラーニング(深層学習)のプログラムを生成するためのソフトウェアであるコアライブラリー「Neural Network Libraries」を無償で公開した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速