7nmプロセスの開発が加速、EUVの導入も現実的に:ファウンドリー各社の動向(2/2 ページ)

ファウンドリー各社の7nmプロセス開発状況

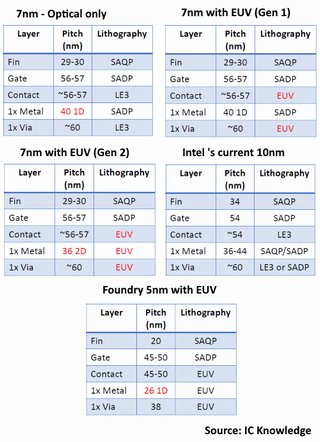

Jones氏の話で最も興味深かった点が、10nm、7nm、5nmプロセスの詳細な分析だ。TSMCは現在、既存の光学ステッパーを用いて、7nmプロセスを適用したチップの量産体制の構築を進めている。GLOBALFOUNDRIESも、同様のプロセスを2018年後半にも強化する計画だ。

両社は2019年初めにEUVを用いて第2世代の7nmプロセスを増強し、コンタクトやビアにEUVリソグラフィを導入する計画だ。これにより、レイヤー数は15から5に低減できるとする。このプロセスでは微細化はされないが、サイクルタイムを短縮するという。さらに、ペリクルも不要である。

GLOBALFOUNDRIESは2017年6月、2019年にEUVリソグラフィを7nmプロセスに導入する計画を発表した。IC KnowledgeのJones氏は、「TSMCも顧客に対し、同様の取り組みを計画していることを非公式に伝えた」と述べた。

半導体メーカーは恐らく、目標とする20mJ/cm2よりも大きい露光量である30mJ/cm2のレジストを用いる必要があるだろう。また、電子ビームシステムを用いてマスクの欠陥を検査するようになるとみられる。

コンタクトとビアにEUVリソグラフィを適用する他、GLOBALFOUNDRIES、Samsung、TSMCは、1xのメタル層を作るためにペリクルを備えたEUVシステムを使う、7nmプロセスの開発を計画している。このプロセスにより、レイヤー数が23から9に削減されるとしている。

こうした手法は、Samsungが2019年に発表する予定の7nmプロセス「7LPP」に導入するものである。TSMCの7nmプロセスは「7FF+」と呼ばれていて、2019年半ばに立ち上がる予定だ。それに続き、2019年後半にはGLOBALFOUNDRIESが7nmプロセス「7LP+」を発表する予定となっている。

Jones氏によると、現在Intelが光学ステッパーを用いて立ち上げ中の10nmプロセスは、Intelのライバル各社が最先端の7nmプロセスと同等のトランジスタ密度を実現できるという。Jones氏は、Intelが2019年には、EUVリソグラフィを導入した10nm以降のプロセスにアップグレードしてくると見込んでいる。

SamsungとTSMCは、2019年末までに利用可能になるであろう5nmプロセスについても既に言及している。

ASMLのJenkins氏は、ASMLが高い開口数に対応する次世代のEUVシステムに向けた光学設計を完成させたと述べた。全体的に非常に優れた設計に仕上がっているという。同社は2016年末、2024年に量産をスタートするシステムに関する計画を発表した。

【翻訳:青山麻由子、編集:EE Times Japan】

関連記事

堅調なTSMC、5nmのリスク生産は19年Q1にも開始

堅調なTSMC、5nmのリスク生産は19年Q1にも開始

TSMCは、半導体メーカーのファブライト化や、HPC(High Performance Computing)向けチップの需要の高まりにより、堅調な成長を続けている。7nmや5nmプロセスの開発も順調だとする。 溶融はんだを注入してバンプ形成、TSVに応用も

溶融はんだを注入してバンプ形成、TSVに応用も

日本アイ・ビー・エム(日本IBM)は「SEMICON Japan 2017」で、溶融はんだをマスクの開口部に直接注入する、はんだバンプ形成技術「IMS(Injection Modled Solder)」の概要を展示した。さらに、IMSをTSV(シリコン貫通電極)に応用する技術も展示。銅めっきを使用するよりも、低コストで短時間にTSVを形成できるとした。 IntelはEUV競争を静観か、導入時期は明言避ける

IntelはEUV競争を静観か、導入時期は明言避ける

EUV(極端紫外線)リソグラフィの開発、導入をめぐって競争を続けてきたIntel、Samsung Electronics、TSMCだが、ここのところIntelは、1歩引いて静観しているようだ。 EUVの量産適用、半導体業界は前向きな見方

EUVの量産適用、半導体業界は前向きな見方

業界団体eBeam Initiativeの調査によると、EUV(極端紫外線)リソグラフィの実用化に対する業界の見方は、だいぶ前向きになっているようだ。 米半導体業界、ポスト・ムーアの技術を模索

米半導体業界、ポスト・ムーアの技術を模索

米国防高等研究計画局(DARPA)は、来たる「ムーアの法則」の終息に備え、“ポスト・ムーア時代”の技術の模索を本格化させている。材料、アーキテクチャ、設計の自動化の3つにターゲットを絞り、まずは2億米ドルを投資してプロジェクトを行う予定だ。 TSMCが10nmプロセスで売り上げを初めて計上

TSMCが10nmプロセスで売り上げを初めて計上

TSMCは、Samsung Electronicsに後れを取っている10nmプロセスで初の売り上げ計上が生じたと明らかにした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ