2xnm技術で試作した40Mビット埋め込みMRAM(前編):福田昭のストレージ通信(109) GFが語る埋め込みメモリと埋め込みMRAM(9)(1/2 ページ)

2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を、前後編で報告する。前編では、高温動作での読み出し電圧マージンの確保と、低温動作での書き込み電圧マージンの維持について紹介する。

配線工程の途中にMTJを形成した40MビットのMRAMマクロ

半導体デバイス技術に関する国際会議「IEDM」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。2017年12月に開催されたIEDMでは、「Memories for the future: device, technologies, and architecture(将来に向けたメモリデバイスの技術とアーキテクチャ)」と題したショートコースが開催された。このショートコースでは6本の技術講座が午前から午後にかけて実施された。

その中から、埋め込みメモリ技術(CMOSロジックとメモリを同じシリコンダイに混載する技術)に関する講座「Embedded MRAM Technology for IoT & Automotive(IoTと自動車に向けた埋め込みMRAM技術)」が興味深かったので、その概要をシリーズでお届けしている。講演者はシリコンファウンダリー(半導体製造請負サービス企業)大手のGLOBALFOUNDRIESでeNVMフェローをつとめるDanny P. Shum氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、SRAM代替用MRAMとフラッシュメモリ代替用MRAMでは、磁気トンネル接合(MTJ:Magnetic Tunneling Junction)の特性がどのように違うのかを説明した。今回と次回は、2xnm世代のCMOSロジック製造技術によって記憶容量が40Mビット(5Mバイト)の埋め込みMRAMマクロを試作した結果を前後編でご報告する。

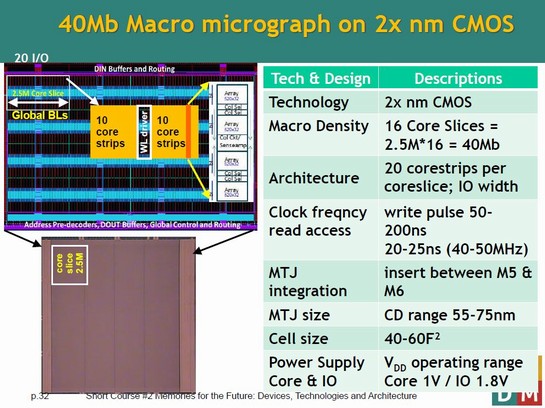

試作した40Mビットの埋め込みMRAMマクロの設計仕様は、以下の通りである。製造技術は300mmウェハーを使った2xnm世代のCMOSロジック技術。読み出しアクセス時間は20ナノ秒〜25ナノ秒、書き込みパルス幅は50ナノ秒〜200ナノ秒、電源電圧はコア電圧が1.0V、IO電圧が1.8Vである。MTJは金属配線の第5層と第6層の間に形成した。MTJのサイズは55nm〜75nm、メモリセル面積(設計寸法換算)は40F2〜60F2となっている。

メモリセルアレイは、2.5Mビットのサブアレイ(コアスライス)が16個である。コアスライスは、コアストリップと呼ぶ20本の細長いセルアレイに分割されている。ワード線ドライバを中央に挟んで、コアストリップを左右に10本ずつレイアウトした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ