マルチコアCPUの“真価”を引き出す自動並列化ソフト:30年の粘りが生んだ(4/4 ページ)

省電力化にも貢献するOSCARTechコンパイラ

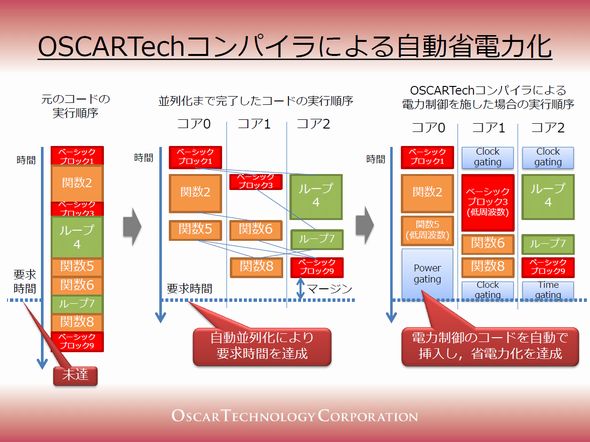

OSCARTechコンパイラは並列化だけでなく、自動省電力化も行うことができる。元のコードを自動並列化した後、処理に要求される時間までのマージン(=何もしていない時間)がある場合、電力制御のコードを自動的に挿入することで省電力化を行う仕組みだ。

OSCARTechコンパイラによる自動省電力化の仕組み。右端の図に「Power gating」「Clock gating」とある通り、クロック周波数を下げたり、電圧を調整したりすることで省電力化を達成する 出典:オスカーテクノロジー(クリックで拡大)

OSCARTechコンパイラによる自動省電力化の仕組み。右端の図に「Power gating」「Clock gating」とある通り、クロック周波数を下げたり、電圧を調整したりすることで省電力化を達成する 出典:オスカーテクノロジー(クリックで拡大)

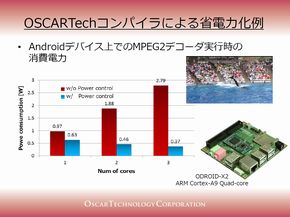

省電力化の事例。左は、Arm「Cortex-9」(クアッドコア)を搭載したボードで検証した結果。電力制御を行った結果は青いグラフ(w/ Power Control)で示されている。右は、「big.LITTLE」構成における省電力化の結果。このような省電力化技術を、スマートフォンなどのモバイル機器に適用できれば、バッテリーの寿命を大きく向上できる可能性はある。 出典:オスカーテクノロジー(クリックで拡大)

省電力化の事例。左は、Arm「Cortex-9」(クアッドコア)を搭載したボードで検証した結果。電力制御を行った結果は青いグラフ(w/ Power Control)で示されている。右は、「big.LITTLE」構成における省電力化の結果。このような省電力化技術を、スマートフォンなどのモバイル機器に適用できれば、バッテリーの寿命を大きく向上できる可能性はある。 出典:オスカーテクノロジー(クリックで拡大)究極のパフォーマンスを引き出すには、チップも自社開発

オスカーテクノロジーは今後のロードマップとして、OSCARTechコンパイラに適したプロセッサの開発も考えている。同社取締役の大橋正尚氏は、「われわれが開発しているソフトウェア並列化技術が、既存のチップに合っているかというと、実はそうでもない」と話す。「CPUとメモリ間で大量のデータを素早く出し入れして演算させるような用途には、既存のチップでも適しているが、緻密な計算がリアルタイムに必要になる制御系の用途では、現行のチップでは、並列化技術を適用してもうまく性能を出せない場合がある。そこがボトルネックになっている」(大橋氏)

そこで、チップも開発してしまおうというのが、オスカーテクノロジーの狙いだ。そのチップとOSCARTechコンパイラを組み合わせることで、究極のパフォーマンスを実現しようとしている。もちろん、実際にチップを製造するとなれば、チップメーカーとの提携は必要になるだろう。「例えば、OSCARTechコンパイラの性能を引き出せるチップの設計情報をIP(Intellectual Property)として提供などの方法が考えられる」と小野氏は述べる。

小野氏は、「OSCARTechコンパイラは、開発コストの削減や省電力の実現や、この技術を応用できる分野の幅広さなどの点から、社会的貢献度の高い技術だと確信している」と語る。オスカーテクノロジーの現在の従業員数は二十数人だ。小野氏は、「人的リソースが足りずに、十分な営業活動やグローバル展開が思うようにできていないといった課題はある」としながらも、OSCARTechコンパイラは質のよい技術であり、その将来性には大いに期待していると強調した。

関連記事

ジャパンパッシングを経て、今再び日本に注目するシリコンバレー

ジャパンパッシングを経て、今再び日本に注目するシリコンバレー

関心を寄せる対象が、日本を通り抜けて他のアジア諸国へと向かってしまう「ジャパンパッシング(Japan Passing)」。だが数年前から、このジャパンパッシングが終息しているともいわれてきた。今回は、1980年代から現在にかけての、日本とシリコンバレーとの関係の歴史を振り返ってみたい。 NEC史上最年少で主席研究員になった天才がもたらした、起死回生のチャンス

NEC史上最年少で主席研究員になった天才がもたらした、起死回生のチャンス

1990年代、シリコンバレーでのコーポレートベンチャリング活動で、うまくいったとは言えないNEC。そこからは、コーポレートベンチャリングに対しては守りの経営が長く続いた。だが、NEC史上最年少で主席研究員となった、ある人物がそれを大きく変えようとしている。 1つのシリコンを使い尽くす ―― 米国半導体メーカーの合理的な工夫

1つのシリコンを使い尽くす ―― 米国半導体メーカーの合理的な工夫

半導体チップ開発は、プロセスの微細化に伴い、より大きな費用が掛かるようになっている。だからこそ、費用を投じて作ったチップをより有効活用することが重要になってきている。そうした中で、米国の半導体メーカーは過去から1つのチップを使い尽くすための工夫を施している。今回はそうした“1つのシリコンを使い尽くす”ための工夫を紹介していく。 NVIDIAが解説するディープラーニングの基礎(前編)

NVIDIAが解説するディープラーニングの基礎(前編)

エヌビディアは2018年4月24日、ディープラーニングに関するセミナー「NVIDIA Deep Learning Seminar 2018」を東京都内で開催した。本稿では、セッション「これから始める人のためのディープラーニング基礎講座」から、ディープラーニングの歴史や概要、学習の流れについて紹介する。 デンソー、自動運転の判断を担う新プロセッサ開発へ

デンソー、自動運転の判断を担う新プロセッサ開発へ

デンソーは2017年8月8日、自動運転システムに向けた新しいプロセッサを開発する子会社を設立すると発表した。CPUやGPUといったプロセッサとは異なる新しいプロセッサを開発し、半導体IPとして広くライセンス販売する計画。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化