AIチップの過去・現在・未来:必要な技術を探る(2/2 ページ)

AIチップの実用化に向けて

近頃これほどAIが話題に上っているのはなぜなのでしょう? このテクノロジーが著しく発展する環境が整ってきたことで、現実世界の問題解決に幅広く役立てられると考える人々が増えているからです。今日ではインターネットによって提供されているインフラのおかげで、世界中の研究者たちが新しいアルゴリズムやソリューションの創造に必要な計算能力、大規模データ、高速通信にアクセスできます。例えば、自動車業界がAI技術に莫大な研究開発費を投じているのは、マシンラーニングによって自動運転などの非常に複雑なタスクを処理できる可能性があるからです。

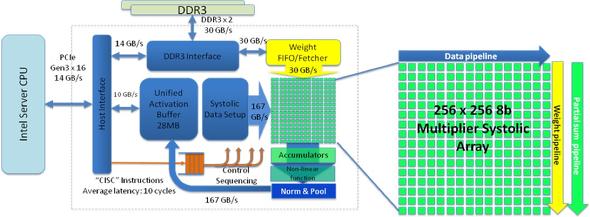

AIチップ設計における最重要課題の一つは全てを集約させることです。ここで言っているのは多種多様なハードウェアアクセラレータを用いてディープラーニングが実装される大規模カスタムSoC(システムオンチップ)のことです。自動車業界の厳格な安全・信頼性要求を考えればなおさらのこと、AIチップの設計は極めて難しいことに違いありません。しかし、AIチップがプロセッシング、メモリ、I/O、インターコネクト技術といった面でいくつか新しいソリューションを取り入れた単なるチップにすぎないのもまた事実です。

新たにIC設計に乗り出したGoogleやTesla、さらにはAIMotiveやHorizon RoboticsといったAIチップベンチャー企業は、ディープラーニングの計算の複雑さについては豊富な知識を持っているものの、こうした最先端SoCを開発するにあたってはいくつもの厳しい試練に直面する可能性があります。これら新規参入プレイヤーができるだけ短期間で実用的なチップを開発できるようにする上では、コンフィギュラブルなインターコネクトIPが重要な役割を果たすと考えられます。

例えば、画像解析による路側物体検出、分類を行う、車のフロントカメラ向けのディープラーニングアクセラレーターを搭載したAIチップについて考えてみましょう。最大帯域幅を確保するために各AIチップに固有のメモリアクセスプロファイルが割り当てられています。パフォーマンス目標を満たす必要があるときはオンチップインターコネクトへのデータフローを最適化して広帯域パスを確保しなければなりませんが、可能な場合は狭いパスを割り当てることによって面積、コスト、消費電力を最適化することができます。より高度なAIアルゴリズムを念頭に置けば各接続も最適化する必要があります。さらに付け加えれば、新しいAIアルゴリズムは毎日生みだされています。ある意味、今日のディープラーニングチップはバナナのようなもので、自分のAIチップに腐ったバナナを、つまり古いアルゴリズムを入れたい人などいないわけです。他の多くの半導体製品と比べてみても、こうした最先端チップでは製品化期間がいっそう重要な意味を持ってくるのです。

AIの未来

ディープラーニングとニューラルネットワークによってAI技術は急速な進歩を遂げていますが、AIの究極の形を実現しようと思ったら根本的に異なるアプローチが必要になってくると考えている研究者たちは大勢います。大半のAIチップは、ルカンやヒントンらによって10年以上も前に発表された概念を絶えず改良してきたものに基づいて設計されており、たとえこのルートに沿って指数関数的な進歩が見られたとしても人間のように考えられるAIを実現できることは到底期待できないからです。

今日私たちが知っているAIは、1つのタスクについてやっとのことで習得したディープラーニングを別の新しいタスクに適用することができません。また、ニューラルネットワークには、予備知識あるいは「アップvsダウン」や「子供には親がいる」というようなルールをうまく組み込むための方法がありません。さらに、人間は記憶に残るたった一度の経験で「熱いストーブには触ってはいけない」ことを学習できるのに対し、ニューラルネットワークに基づくAIに学習させるためには膨大な例が必要となります。大量のデータセットを使うことなく現在のAI技術をさまざまな問題にどう適用していけるのかは依然としてはっきりしていません。

今のところAIチップは標準的な人間に比べてそう賢いわけではありませんが、それ自体が賢いことは確かであり、この先ますます賢くなっていくことはまず間違いないでしょう。AIチップが半導体プロセス技術、コンピュータアーキテクチャ、SoC設計の進歩を促すことによって処理能力が格段に上がれば、次世代AIアルゴリズムが登場するのもそう遠いことではないでしょう。また同時に、それら新しいAIチップの独自ハードウェアアクセラレーターにディープラーニングに必要なデータストリームを絶えず供給するためには、高度なメモリシステムとオンチップインターコネクトアーキテクチャが必要不可欠だと言えます。

筆者プロフィール

Ty Garibay / Arteris IP、最高技術責任者(CTO)

Motorola、Cyrix、 SGI、 Alchemy Semiconductorの各社でアーキテクチャと設計を主導し、マイクロプロセッサ/SoCアーキテクチャおよび技術の開発において中心的役割を果たしてきました。Armのオースティン設計センターでTexas InstrumentsのOMAPアプリケーションプロセッサグループ向けArmコア開発およびICエンジニアリグを指揮した経験もあります。

Arteris IP入社前はAlteraのICエンジニアリング部門バイスプレジデントを務め、その後はインテルのプログラマブルソリューショングループでFPGA設計を主導してきました。単独/共同合わせて34の特許を取得しており、その功績は多数の技術誌や会議で取り上げられています。

関連記事

中堅研究員はAIの向こう側に何を見つけたのか

中堅研究員はAIの向こう側に何を見つけたのか

約2年続いてきた本連載も、いよいよ最終回です。「中堅研究員はAIの向こう側に“知能”の夢を見るか」と名付けた第1回から2年間。筆者が“AIの向こう側”に見つけたものとは、何だったのでしょうか。 AIの開発、半導体業界にとってますます重要に

AIの開発、半導体業界にとってますます重要に

どの半導体メーカーが、何らかの形でAI(人工知能)分野に携わっているのかは、簡単にリストアップすることができる。ほぼ全てのメーカーが該当するからだ。機械学習(マシンラーニング)は、幅広い可能性を秘めているため、ほとんどの半導体チップメーカーが研究に取り組んでいる状況にある。 車載半導体設計者がADASから学ぶべき教訓

車載半導体設計者がADASから学ぶべき教訓

自動運転システムは、さまざまな課題を設計エンジニアらに突きつけています。そうした中で、半導体開発者がADAS(先進運転支援システム)の進化から学べることは数多くあります。過去数年の間に自動車分野の開発者らがADAS設計の効率化を図っていく中で学んできた3つの主な教訓を紹介します。 ADAS設計のハードへの移行が自動運転の未来を変える

ADAS設計のハードへの移行が自動運転の未来を変える

自動運転の実現へ期待が集まるが、自動運転システムの実現にはさらなるソフトウェア開発規模の増大という大きな課題がある。この大きな課題を解決するには、ソフトウェア中心のアプローチからカスタムハードウェア開発へと重心を移すべきではないだろうか。 悪いけど、IPはEDAじゃないよ

悪いけど、IPはEDAじゃないよ

半導体IPビジネスとEDAビジネスを比べている会話を耳にした。彼らは「IPはEDA」だという結論に達した。しかし、いくつかの関連性はあるものの、これらはまったく異なる代物だ。それぞれの分野で10年間を費やした私は、このことを学んだ。 SoC設計者が“ポスト・ムーアの法則時代”を生き抜く術

SoC設計者が“ポスト・ムーアの法則時代”を生き抜く術

チップ設計者に「タダ飯」をごちそうしてくれた“ムーアの法則”がなくなろうとしている。これからチップ設計者が生きていくには性能向上と消費電力低減を実現する革新的方法を自ら生み出していくしかない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速