メモリセルアレイのベースとなるマルチペア薄膜の形成:福田昭のストレージ通信(119) 3D NANDのスケーリング(7)(1/2 ページ)

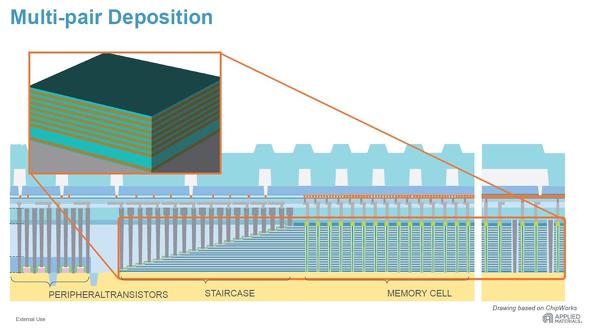

3D NANDフラッシュメモリの製造プロセスにおける重要な技術の一つであるマルチペア(Multi-pair)薄膜の成膜(Deposition)」を解説する。

絶縁層と制御ゲート層で薄膜のペアを構成

半導体メモリ技術に関する国際会議「IMW(International Memory Workshop)」では、カンファレンスの前日に「ショートコース(Short Course)」と呼ぶ1日間のセミナーを開催している。今年(2018年)5月に開催されたIMWのショートコースでは、9件の技術講座(チュートリアル)が午前から午後にかけて実施された。その中から、3D NANDフラッシュメモリ技術に関する講座「Materials, Processes, Equipment Perspectives of 3D NAND Technology and Its Scaling(3D NAND技術とそのスケーリングに関する材料とプロセス、製造装置の展望)」がとても参考になったので、その概要をシリーズでお届けしている。講演者は半導体製造装置の大手ベンダーApplied MaterialsのSean Kang氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、3D NANDフラッシュメモリの製造プロセスにおける重要な技術(キープロセス)を概観した。今回は、キープロセスの1つである、「マルチペア(Multi-pair)薄膜の成膜(Deposition)」に関する技術を説明していこう。

ここでペア薄膜とは、絶縁層と制御ゲート層(ワード線層)の薄膜を指す。3D NANDフラッシュメモリの製造工程では、このペア薄膜を数多く積み上げることで、数多くのメモリセルの連なりである、セルストリングを形成する。数多くのペア薄膜を均一な品質と膜厚で堆積することが欠かせない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」