10nmで苦戦するIntel、問題はCo配線とRuバリアメタルか:湯之上隆のナノフォーカス(9)(3/5 ページ)

多層配線の構造とCu配線の限界

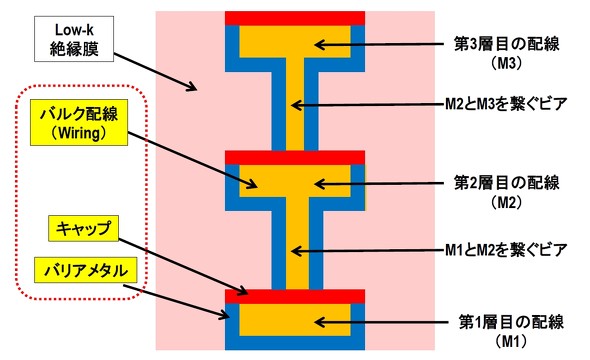

多層配線の構造を図3に示す。現在、ロジックチップの多層配線は、12層程度あり、配線および上下の配線間をつなぐビアを同時に加工するデュアルダマシンというプロセスで形成されている。その配線を形成する要素は、バルク配線、バリアメタル、キャップメタルの三つである。

2000年頃までは、バルク配線材料としてアルミニウム(Al)が使われていたが、配線の微細化とともに配線抵抗が増大し、信号遅延が起きることが明らかになったため、Alより抵抗値の小さなCuが使われるようになった。

Cuは絶縁膜中を拡散してしまうため、それを防ぐためにTa(タンタル)やTaN(窒化タンタル)などのバリアメタルを形成する必要がある。また、Ta(N)は、Cuと絶縁膜を接着させる役目も担っている。さらに、Cu配線のエレクトロマイグレーションを防止する効果などがあることから、キャップメタルを形成している。

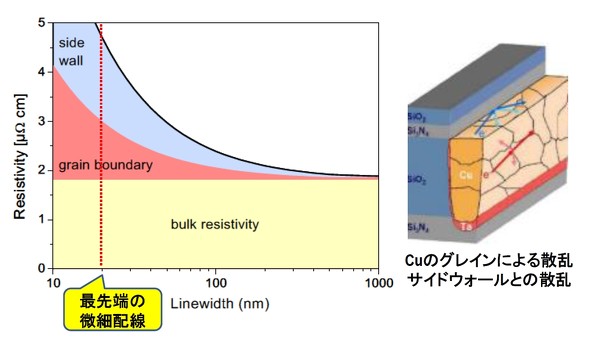

ところが、配線の微細化するにつれて、Cu配線およびTa(N)バリアメタルの限界が見えてきた。IBMの野上毅氏が2017年のVLSIシンポジウムで発表した資料によれば、Cu配線の微細化とともに、配線を移動する電子がCu配線のグレインバウンダリで衝突し、さらにTa(N)などのサイドウオールに衝突するために、抵抗値が増大し、信号遅延が避けられない事態となったのである(図4)。

例えば、配線幅が20nmになると、配線の抵抗値は、Cuのバルク抵抗値の2.5倍以上になる。そして、この傾向は、配線の微細化とともに、より深刻さを増す。以上の理由から、半導体の微細化を推進するためには、Cuに変わる配線材料と、Ta(N)に変わるバリアメタルを探索することが必要となっていた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速