日立、CMOSアニーリングマシンを名刺形状で実現:エネルギー効率は従来の約17万倍

日立製作所は、従来型コンピュータに比べて処理性能を約2万倍、エネルギー効率を約17万倍に高めた名刺サイズのCMOSアニーリングマシンを開発した。

スマホなどで組み合わせ最適化問題の計算が可能に

日立製作所は2019年2月、従来型コンピュータに比べて処理性能を約2万倍、エネルギー効率を約17万倍に高めた名刺サイズのCMOSアニーリングマシンを開発したと発表した。集積度を高める回路技術とチップ間接続技術を新たに開発することで実現した。

CMOSアニーリングマシンは、イジングモデルを用いて組み合せ最適化問題を解くために開発している新型コンピュータ。同社はこれまで、FPGAを用いたCMOSアニーリングチップを25個接続して、10万2400パラメーターの問題に対応できるCMOSアニーリングマシンを開発してきた。パートナー向けにクライドサービスも2018年8月より提供している。

今回は、CMOSアニーリングマシンをスマートフォンやカメラ、センサーなどのIoT(モノのインターネット)機器に実装し、エッジ側で組み合わせ最適化問題の計算をリアルタイムに処理する用途を視野に入れて開発した。

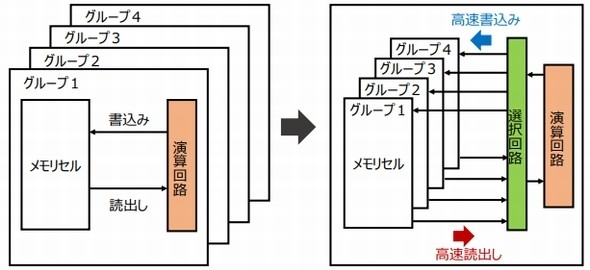

これを可能にするため、日立は大きく2つの技術を開発した。その1つが「高集積化を実現するための回路技術」である。CMOSアニーリングマシンの最適化問題を計算するためにこれまで、パラメーターを4グループに分け、グループごとに順次計算していた。このため、パラメーターグループの数だけ演算回路を用意する必要があった。

今回、パラメーター値を保持するメモリセルに対して、高速にアクセスする技術を開発した。これにより、1つの演算回路で演算順序に従い、4つのパラメーターグループを切り替えながら共有することが可能となった。演算回路数を削減できることで、メモリセルの集積度は従来の1.5倍となり、1チップで3万976のパラメーターを集積することに成功した。

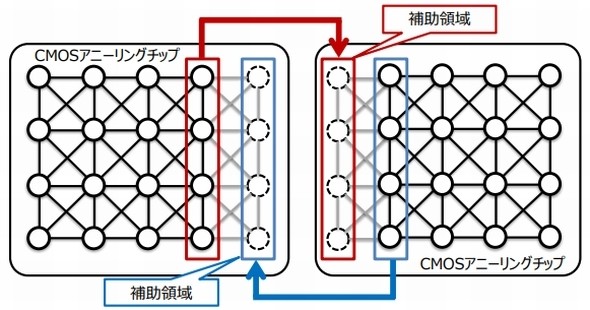

もう1つは「高速計算を可能にするチップ間接続技術」である。最適化問題の計算は、個々のパラメーター値と、それに隣接するパラメーター値を用いて計算する。このため、半導体チップ間でパラメーター値を転送する必要がある。従来はこの時に遅延が生じていた。

これを解決するため、新たなチップ間接続技術を開発した。半導体チップの端部に、別チップのパラメーター値をコピーするための補助領域を設けた。これにより、あるパラメーターグループを計算している間に、次のパラメーターグループをコピーしておくことができるという。

これらの技術を適用して開発したチップ2個を接続し、外形寸法が91×55mmのCMOSアニーリングマシンを開発した。ランダムに生成したイジングモデルのアニーリング計算を実行し、その性能を検証した。約6万パラメーターの組み合わせ最適化問題の計算を行ったところ、従来型コンピュータに比べて処理性能は約2万倍、エネルギー効率は約17万倍となった。

なお研究成果の一部を、半導体集積回路技術の国際会議「ISSCC(International Solid-State Circuits Conference) 2019」(2019年2月17~21日、米国カリフォルニア州サンフランシスコ)で発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -- EE Times Japanテ勇DN Japan 邨ア蜷磯崕蟄千沿�壼刈騾溘☆繧九後ぎ繝ゥ繧ケ蝓コ譚ソ縲埼幕逋コ縲譌・譛ャ繧ゅ¢繧灘シ募スケ縺ォ窶補� 髮サ蟄千沿2025蟷エ4譛亥捷

- 髢狗匱繧堤ー。邏�蛹悶@遶カ莠牙鴨繧貞シキ蛹悶☆繧九∫ャャ4荳紋サ」豎守畑USB繝�ヰ繧、繧ケ繧ウ繝ウ繝医Ο繝シ繝ゥ繝シ縺ョ螳溷鴨

- 蜊雁ー惹ス謎ク崎憶隗」譫舌�譁ー蠅�慍縲√�繝ュ繧サ繧ケ髢狗匱繧貞刈騾溘☆繧区ャ。荳紋サ」縺ョ3D X邱夐。募セョ髀。縺ョ螳溷鴨

- 縲悟屓謚倥さ繝ウ繝医Λ繧ケ繝医ヨ繝「繧ー繝ゥ繝輔ぅ縲阪r遐皮ゥカ螳、繝ャ繝吶Ν縺ァ螳溽樟縺吶k譁ケ豕輔→縺ッ��

- 蜊雁ー惹ス灘膚遉セ 讌ュ邵セ縺セ縺ィ繧√�2025蟷エ3譛域悄隨ャ3蝗帛濠譛溘�

Special Contents 2

- PR -記事ランキング

- 半導体メーカーの「悲喜こもごも」 絶好調のTSMC、人員削減のST

- IntelがAltera売却へ、株式51%を米投資ファンドに

- 2024年の半導体市場は21%成長 NVIDIAが初の首位に

- 世界半導体市場が10カ月連続で17%以上成長 2月として過去最高に

- ミネベアミツミが芝浦電子買収へ 「8本槍」戦略強化に向け

- チップに「水路」を作り冷却液を流し込む 高効率に放熱

- 2035年のウエハー需要を予測する ~半導体も「VUCA時代」に

- AIのデータ転送問題解決に王手、シリコンフォトニクス新興企業

- トランプ政権の「アメとムチ」 Intelは補助金を受け取れるのか

- 1インチサイズの全固体電池を10秒で作製 レーザーで加工

高集積化に向けた回路技術の概略 出典:日立

高集積化に向けた回路技術の概略 出典:日立 チップ間接続の概略 出典:日立

チップ間接続の概略 出典:日立 開発したCMOSアニーリングマシンの外観 出典:日立

開発したCMOSアニーリングマシンの外観 出典:日立 車載制御マイコン、ハードによる仮想化が可能に

車載制御マイコン、ハードによる仮想化が可能に 東工大、極低消費電力のデジタルPLLを開発

東工大、極低消費電力のデジタルPLLを開発 広島大学ら、300GHz帯トランシーバーICを開発

広島大学ら、300GHz帯トランシーバーICを開発 ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない?

ISSCC 2019の目玉はAIと5Gに、CPUの話題は少ない? 日立、演算規模が可変なCMOSアニーリングマシンを開発

日立、演算規模が可変なCMOSアニーリングマシンを開発 日立、新構造のSiCパワーデバイス「TED-MOS」を発表

日立、新構造のSiCパワーデバイス「TED-MOS」を発表