半導体業界のトレンドは「3次元化」が明確に VLSI 2019:過去最高の出席者数で大盛況(2/4 ページ)

選択的ALDやALE

ALPに関するSunday Workshop1では、6件の発表があった。その中のRobert D. Clark氏(Tokyo Electron Technology Center)およびErwin Kessels氏(Eindhoven Univ. of Tech.)の発表資料を基に、ALDとALEの概要を説明し、実際にどのようなプロセスが可能になるかを紹介したい。

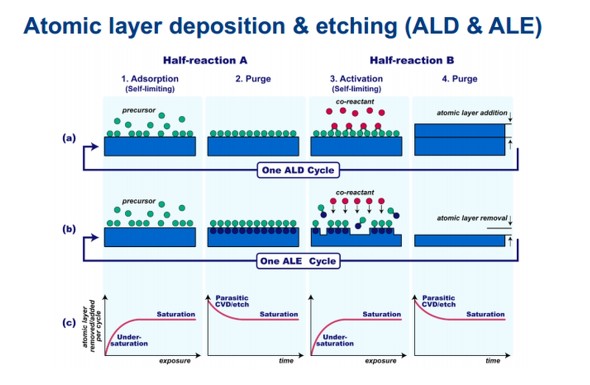

図3に示したように、ALDでは原子層一層ずつ成膜することができる。また、ALEでは、原子層を一層ずつエッチングすることができる。

図3 ALDとALEのプロセスフロー 出典:E. Kessels, Eindhoven Univ. of Tech.” Plasma-Based Selective Atomic Layer Deposition and Etching to Enable 5nm and Beyond Device Technology”, Sunday Workshop1, VLSI2019より引用(クリックで拡大)

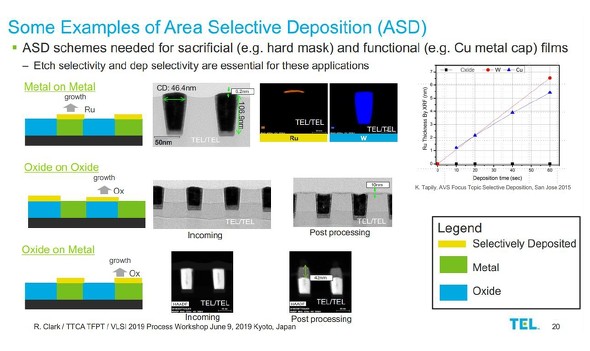

図3 ALDとALEのプロセスフロー 出典:E. Kessels, Eindhoven Univ. of Tech.” Plasma-Based Selective Atomic Layer Deposition and Etching to Enable 5nm and Beyond Device Technology”, Sunday Workshop1, VLSI2019より引用(クリックで拡大)さらに、ALDにおいては、金属上に金属を成膜する“Metal on Metal”、絶縁膜上に絶縁膜を成膜する“Oxide on Oxide”、絶縁膜上に金属を成膜する”Metal on Oxide”など、選択的な成膜が可能になる(図4)。

図4 Area Selective Deposition(ASD) 出典:R. Clark, TEL.” Selective and Self-Limited Thin Film Processes for the Atomic Scale Era”, Sunday Workshop1, VLSI2019より引用(クリックで拡大)

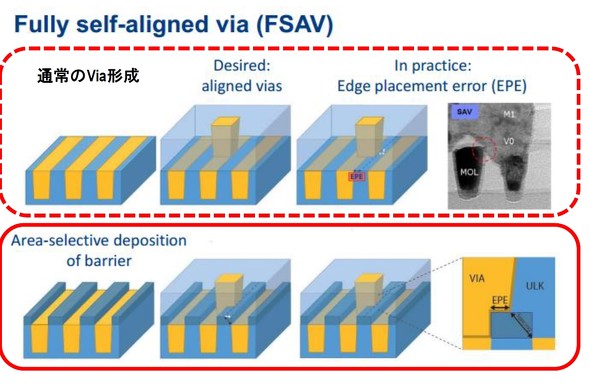

図4 Area Selective Deposition(ASD) 出典:R. Clark, TEL.” Selective and Self-Limited Thin Film Processes for the Atomic Scale Era”, Sunday Workshop1, VLSI2019より引用(クリックで拡大)実際に、“Metal on Metal”を適用したSelf-Aligned Via(セルフアラインビア)を図5に示す。通常のビア形成では、アライメントのずれにより、隣のラインとショートする場合がある。ここで、メタル配線を隔てるLow-k上に、選択的にバリアを成膜した後にビアを形成すると、上記のようなショートを防止することができる。

図5 Self-aligned via(セルフアラインビア) 出典:E. Kessels, Eindhoven Univ. of Tech.” Plasma-Based Selective Atomic Layer Deposition and Etching to Enable 5nm and Beyond Device Technology”, Sunday Workshop1, VLSI2019より引用(クリックで拡大)

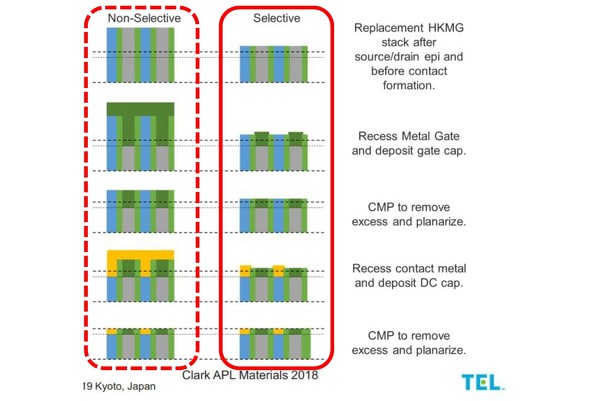

図5 Self-aligned via(セルフアラインビア) 出典:E. Kessels, Eindhoven Univ. of Tech.” Plasma-Based Selective Atomic Layer Deposition and Etching to Enable 5nm and Beyond Device Technology”, Sunday Workshop1, VLSI2019より引用(クリックで拡大)また、High-k/Metal Gate(HKMG)の形成に、選択的ALDを適用したケースを図6に示す。通常のHKMGのプロセスと比較すると、成膜量を大幅に減少することができるため、CMP(化学的機械研磨)で除去する量も減少する。その結果、スループットが格段に向上する上、コスト削減にもつながる。

図6 Area Selective Deposition(ASD)を利用したHKMG 出典:R. Clark, TEL.” Selective and Self-Limited Thin Film Processes for the Atomic Scale Era”, Sunday Workshop1, VLSI2019より引用(クリックで拡大)

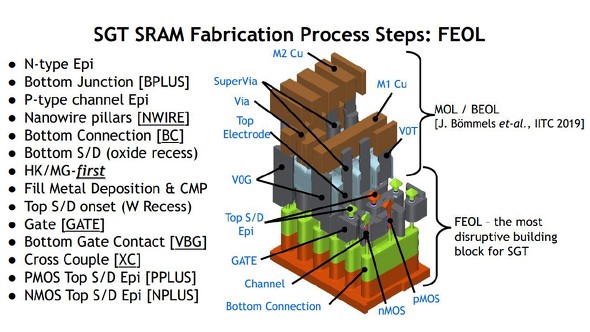

図6 Area Selective Deposition(ASD)を利用したHKMG 出典:R. Clark, TEL.” Selective and Self-Limited Thin Film Processes for the Atomic Scale Era”, Sunday Workshop1, VLSI2019より引用(クリックで拡大)6月13日(木)のTechnology Symposiumの“T15: Advanced FinFET & GAA?”にて、imecのMin-Soo KIM氏が、“12-EUV Layer Surrounding Gate Transistor (SGT) for Vertical 6-T SRAM: 5-nm-class Technology for Ultra-Density Logic Devices”と題する発表を行った。

フロントエンドに12工程ものEUVを使った5nmクラスのGate All Aroud(GAA)構造のトランジスタは、極めて微細かつ複雑である(図7)。このようなトランジスタの形成には、選択的ALDやALEが大いに効果を発揮すると期待している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」