半導体業界のトレンドは「3次元化」が明確に VLSI 2019:過去最高の出席者数で大盛況(3/4 ページ)

656人が出席したShort Course

2日目の6月10日(月)には、以下の三つのShort Courseが行われた。カッコ内はVLSI事務局が発表した各Short Courseの登録者数である。

- CMOS Technology Enablers for Pushing the Limits of Semiconductors: Materials to Packaging(273人)

- Advanced 5G Circuits, Systems and Applications(114人)

- Opportunities and Challenges at the Intersection of Security and AI(174人)

以上に加えて、全てのShort Courseに登録した人が203人おり、これらを合計すると659人と過去最高を記録した。

Short Courseの出席者数は、ここ10年間で約2.4倍に増加した。この理由を次のように考えている。筆者の予想では、Short Courseの出席者には、装置メーカーや材料メーカーの技術者などが多いのではないかと思う。というのは、Technical Sessionでは、英語の論文を読み、英語の講演を聞かなければ、内容を理解することが困難である。これは、非常にハードルが高い。

一方、Short Courseでは、ホットなトピックスを一日集中して聞くことができる。その上、発表スライドの全てがPDFで配布されるため、英語の文章を読まなくても、図を見ればおおよその概要が理解できる。そのため、装置メーカーや材料メーカーにとってShort Courseは、格好の情報収集の機会となるからだ。

半導体の技術トレンド

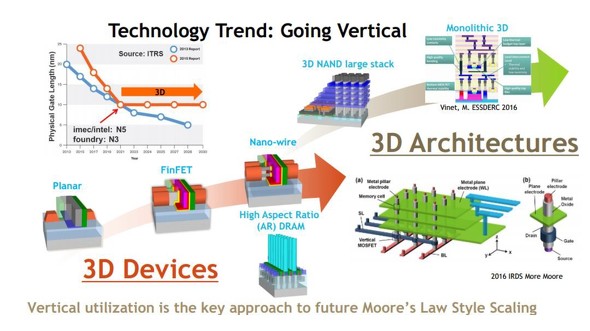

筆者は、CMOS Technology関係のShort Course1に参加した。そこから見えてきた技術トレンドは、半導体デバイスは3次元化し、そしてチップを複数枚重ねる3次元アーキテクチャ化が進むだろうということだ(図8)。

図8 半導体の技術トレンド:3D Devicesから3D Architectures 出典:R. Clark, TEL, “Advanced Process Technologies Required for Future Scaling and Devices”, Short Course1, VLSI2019より引用(クリックで拡大)

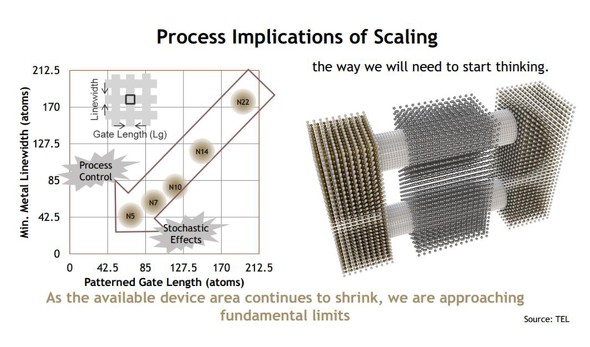

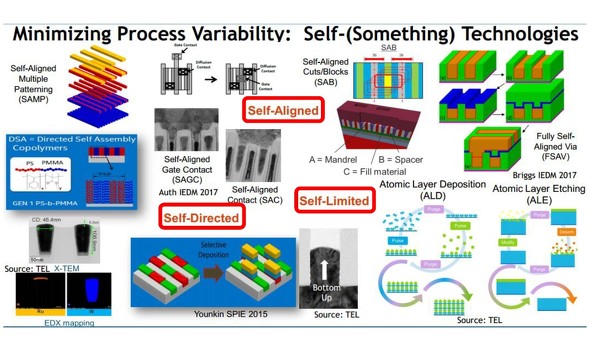

図8 半導体の技術トレンド:3D Devicesから3D Architectures 出典:R. Clark, TEL, “Advanced Process Technologies Required for Future Scaling and Devices”, Short Course1, VLSI2019より引用(クリックで拡大)しかし、微細化を続けるには、相当に難しい技術開発が待ち受けている。例えば、5nmノードの微細配線幅には、原子がたったの42.5個しかない(図9)。このような微細配線を形成するには、Self-Directedな成膜、Self-Limitedなエッチング、そしてSelf-Alignedな構造を駆使する必要があるだろう(図10)。

図9 ゲート長および微細配線の幅と原子数の関係 出典:R. Clark, TEL, “Advanced Process Technologies Required for Future Scaling and Devices”, Short Course1, VLSI2019より引用(クリックで拡大)

図9 ゲート長および微細配線の幅と原子数の関係 出典:R. Clark, TEL, “Advanced Process Technologies Required for Future Scaling and Devices”, Short Course1, VLSI2019より引用(クリックで拡大) 図10 Self-Directed、Self-Limited、Self-Alignedがキーワード 出典:R. Clark, TEL, “Advanced Process Technologies Required for Future Scaling and Devices”, Short Course1, VLSI2019より引用(クリックで拡大)

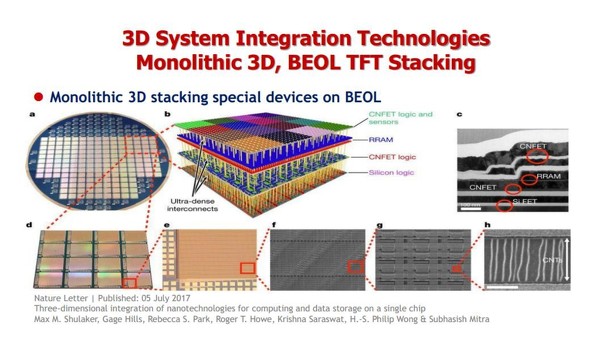

図10 Self-Directed、Self-Limited、Self-Alignedがキーワード 出典:R. Clark, TEL, “Advanced Process Technologies Required for Future Scaling and Devices”, Short Course1, VLSI2019より引用(クリックで拡大)そして、さまざまなチップを重ねる3次元アーキテクチャが当たり前のように使われると考えられる。図11は、TSMCのチップ積層技術である。複数枚のロジックチップやメモリを3次元方向に積層し、Through-Silicon Via(TSV)を開けてCuでチップ間をつないでいる。

図11 TSMCの3次元インテグレーション技術 出典:C. H. Tung, TSMC, “3D Integration for More-Moore and More-than-Moore”, Short Course1, VLSI2019より引用(クリックで拡大)

図11 TSMCの3次元インテグレーション技術 出典:C. H. Tung, TSMC, “3D Integration for More-Moore and More-than-Moore”, Short Course1, VLSI2019より引用(クリックで拡大)TSMCは、“Chip on Chip”、”Chip on Wafer”および、”Wafer on Wafer”技術も開発しており、これらを”Wafer Level System Integration”、略して“WLSI”と呼称していた。なかなかしゃれたネーミングである。

微細化はスローダウンするかもしれないが、今後は、上記のようなデバイスの3次元化とチップを積層する3次元化が、ムーアの法則をけん引していくと思われる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- わずか3個のLSIでモバイル超音波診断装置を実現、ソシオネクスト

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術