ビアスイッチでプログラムするFPGAチップを開発:実装密度を従来の12倍に向上

大阪大学の橋本昌宜教授らによる研究グループは、配線層内に設けたビアスイッチで論理機能をプログラムする「ビアスイッチFPGAチップ」を開発した。

AI処理に適したFPGAアーキテクチャも開発

大阪大学大学院情報科学研究科の橋本昌宜教授らによる研究グループは2020年2月、配線層内に設けたビアスイッチで論理機能をプログラムする「ビアスイッチFPGAチップ」を開発したと発表した。また、AI(人工知能)処理に適したFPGAアーキテクチャも開発した。

一般的なFPGAは、プログラム素子にSRAMや不揮発性メモリを用いている。機器に実装した後でも、現場でこれらのデータを書き換え、回路を再構成することで機能を変更することができる。

これに対し、最小線幅65nmのCMOSプロセスを用いて試作したFPGAは、新たに開発した「ビアスイッチ」と呼ぶ不揮発性スイッチデバイスを用いている。ビアスイッチは、配線層内に設けた不揮発スイッチ(原子スイッチ)とプログラム用の選択デバイス(バリスター)で構成されている。

原子スイッチは、スイッチ機能と不揮発メモリ機能を合わせ持つ。金属原子が固体電解質内を移動してスイッチするため、「低抵抗で低入力容量」という特長がある。バリスターは、ビアスイッチアレイの中で、選択したビアスイッチのみをプログラムするために用いる。「抵抗が低電圧印加の時に高く、高電圧印加の時に低い」という特長がある。

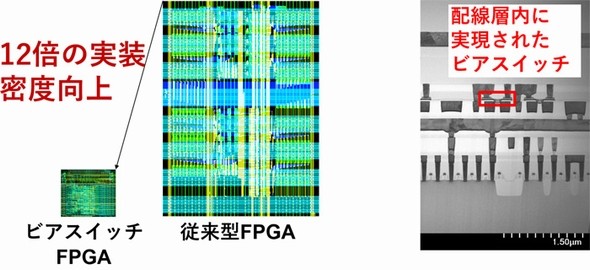

ビアスイッチを用いたFPGAは、トランジスタでプログラム機能を実現していた従来のFPGAに比べ、実装密度を12倍向上できることを実証した。これにより、チップ面積が小さくなり、製造コストを大幅に削減できる可能性があるという。あるいはプログラム用途に向けていたトランジスタを、全て演算処理に活用することでチップ性能を向上できるとみている。

研究グループは、AI処理を効率良く実行するFPGAアーキテクチャも開発した。その性能を予測したところ、従来の一般的なFPGAに比べ、エネルギー効率が5倍も向上することが分かった。7nmのCMOSプロセスでFPGAを製造すると、11倍のエネルギー効率を達成できるという。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 2

- PR -記事ランキング

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- 「NVIDIAと真逆の取り組みをしよう」 Jim Keller氏

- JDIの液晶の知見、先端半導体パッケージングの中核技術に

- 「本当に安全なのか」 中国の機器や部品を見直すべき

- キオクシアの年度業績、3年ぶりの黒字転換で過去2番目の営業利益を計上

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- キオクシアのNAND戦略 「BiCS FLASH」はどう進化するのか

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- 世界半導体市場は12カ月連続で成長、前月比では米州と日本が減少

- 自律神経から「頑張りすぎ」を可視化、村田製作所

開発したビアスイッチFPGAと従来型FPGAの実装密度比較および、配線断面写真 出典:大阪大学他

開発したビアスイッチFPGAと従来型FPGAの実装密度比較および、配線断面写真 出典:大阪大学他 大阪大ら、環状構造の有機EL発光材料を開発

大阪大ら、環状構造の有機EL発光材料を開発 大阪大学とローム、テラヘルツ波の検出感度1万倍

大阪大学とローム、テラヘルツ波の検出感度1万倍 有機半導体の分子形状を物理吸着で一斉に制御

有機半導体の分子形状を物理吸着で一斉に制御 東北大ら、超伝導体をトポロジカル超伝導体に変換

東北大ら、超伝導体をトポロジカル超伝導体に変換 フレキシブルひずみセンサー、ゲージ率は200倍

フレキシブルひずみセンサー、ゲージ率は200倍 阪大ら、生体計測用の有機差動増幅回路を開発

阪大ら、生体計測用の有機差動増幅回路を開発