半導体パッケージ基板の技術ロードマップ:福田昭のデバイス通信(263) 2019年度版実装技術ロードマップ(71)(2/2 ページ)

ビルドアップ構造の量産基板は配線幅/間隔で10μm/10μmがほぼ限界

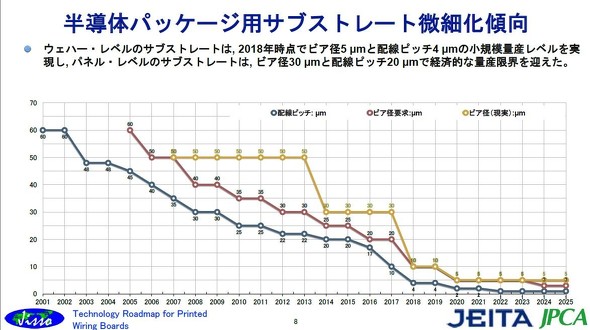

半導体パッケージ基板は、プリント配線板の微細化をけん引してきた。しかしここに来て微細化の壁に突き当たりつつある。微細化をけん引していたのは過去にはリジッド配線板プロセスとセラミック基板プロセスだった。最近はビルドアップ配線板が微細化を主導してきた。

経済性を考慮すると、配線幅(導体幅)/間隔で10μm/10μmが現在のところ、ほぼ量産の限界だとされる。さらなる微細化をけん引するのは従来のプリント配線板製造技術ではなく、半導体製造技術だと考えられる。

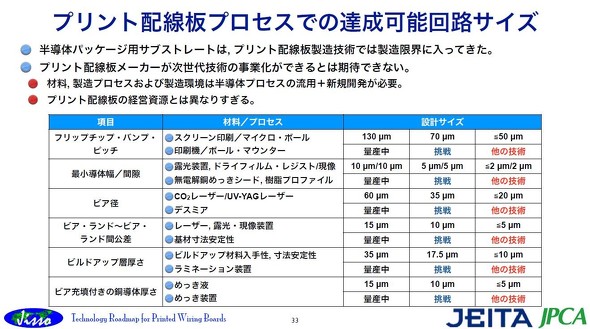

ただし、ある程度のコスト増を許容すると、ビルドアップ構造を含めたプリント配線板技術でもいくらかの微細化と高密度化が見込める。例えばフリップチップのバンプピッチでは130nmピッチが量産中であり、次の70nmピッチが従来技術の改良による目標となる。配線幅(導体幅)/間隔では10μm/10μmが量産中であり、次の目標は5μm/5μmである。ビア径は60μmが量産中であり、35μmが次の目標だ。

次世代の微細配線製造技術で0.5μm/0.5μmを目指す

さらに微細化と高密度化を進めるには、次世代の微細配線板製造技術が必要とされる。その候補を挙げると、「ビルドアップ基板と薄膜インターポーザーの組み合わせ」「ガラス基板(ガラスサブストレート)」「ウエハーレベル基板(シリコン基板)」「緩やかな配線ピッチのシリコンインターポーザー(ラフピッチ・シリコンインターポーザー)」「微細な配線ピッチのシリコンインターポーザー(ファインピッチインターポーザー)」がある。

これらの次世代技術によって配線幅(導体幅)/間隔で2μm/2μm、さらには0.5μm/0.5μmという極めて微細な配線の実現を目指す。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

筐体や衣服などとの融合を目指す新世代の配線板技術

筐体や衣服などとの融合を目指す新世代の配線板技術

今回は、異なる製造技術によって付加価値を高める技術「ストレッチャブル配線板」「コンフォーマブルエレクトロニクス」「テキスタイルエレクトロニクス」の3つを取り上げる。 小型化と薄型化、多機能化を後押しする部品内蔵基板

小型化と薄型化、多機能化を後押しする部品内蔵基板

今回は、新世代のプリント配線板を代表する「機能集積基板」の概要を解説する。半導体チップや受動部品などを内蔵することで複数の機能を持たせた基板である。 プリント配線板の性能を大きく左右する絶縁材料

プリント配線板の性能を大きく左右する絶縁材料

プリント配線板では多種多様な絶縁基材が使われる。新世代のプリント配線板が採用した新しい絶縁基材について解説する。 変革期を迎えたプリント配線板技術

変革期を迎えたプリント配線板技術

今回から、第5章「プリント配線板」の概要を解説していく。まずは伝統的なプリント配線板の用語と製造方法を紹介しよう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- Rapidus、シリコンバレーに新会社設立 AI半導体の顧客開拓を加速

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化