新手法の酸化膜形成でSiC-MOSFETの性能が10倍に:30年来の課題に光明(4/4 ページ)

SiC-MOSFETのコストが数分の1に

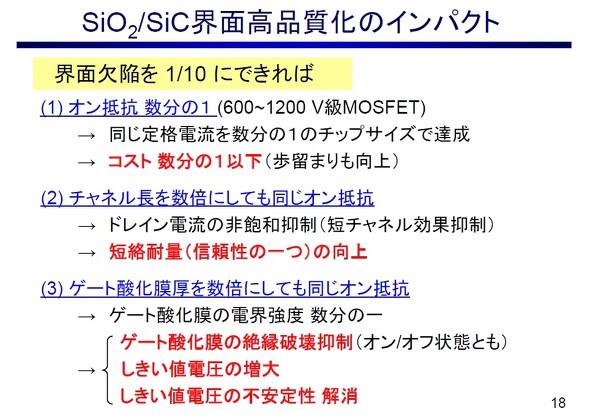

界面欠陥が10分の1に低減したことによる具体的な効果としては、600V〜1200VクラスのSiC-MOSFETにおいて、オン抵抗が数分の1になる。つまり、同じ定格電流を数分の1(2分の1、3分の1)のチップサイズで達成できるようになるので、コストが数分の1になる。「SiCパワーデバイスではコストが高いというのが課題の一つなので、これを従来の2分の1、3分の1にできるということだ」(木本氏)

その他、チャネル長を数倍、ゲート酸化膜を数倍にしてもオン抵抗が同等レベルに抑えられるので、信頼性の向上につながる。

新手法は、特殊な装置や高価な原材料は一切要らないので、導入もしやすい。猛毒のNOガスを使わずに済むのも利点だ。「製法の障壁は特にないと考えている。大面積のウエハーにSiを均一に堆積させる必要はあるが、(主流の)6インチSiCウエハーや、あるいは300mmSiCウエハーでも問題ないのではないか。タクトタイムについても、百数十枚のウエハーをバッチ処理できるのであまり心配はしていない」(木本氏)

現時点では、この新手法を実際に採用してSiC-MOSFETを量産する具体的な計画はまだないが、「採用してくれるメーカーがあれば、1〜2年で量産を実現できるのではないか」と木本氏は見ている。

実は、「SiCウエハー上にSiを堆積して酸化する」方法は、以前に米国で考案され、プロセス技術として特許も取得されているという。木本氏は「ただ、その手法では、750℃ではなく900℃で酸化させている。従ってSiCの表面も酸化してしまい、うまくいかなかったようで、同手法は実際の量産に採用されていないようだ」と語る。木本氏らは、今回提案した新しい手法を、構造特許として出願済みだ。

関連記事

新デバイス構造でSiC MOSFETの信頼性を向上

新デバイス構造でSiC MOSFETの信頼性を向上

東芝デバイス&ストレージは、SiC MOSFETの内部にSBDを搭載する新たなデバイス構造を開発した。従来技術に比べて、オン抵抗の上昇を抑えつつSiC MOSFETの信頼性を10倍以上も高めることが可能だという。 パワー半導体市場、2030年に4兆円超の規模へ

パワー半導体市場、2030年に4兆円超の規模へ

富士経済は、世界のパワー半導体市場を調査し、2030年までの市場予測を発表した。これによると、2019年の2兆9141億円に対し、2030年は4兆2652億円に達すると予測した。 パワー半導体世界市場、2025年に243億5100万ドルに

パワー半導体世界市場、2025年に243億5100万ドルに

矢野経済研究所は2020年7月27日、パワー半導体の世界市場予測を発表した。新型コロナウイルス感染症(COVID-19)の影響でパワー半導体の世界市場は2020年にマイナス成長を見せるものの、2021年に一部分野から回復基調に転じ、2025年には243億5100万米ドルにまで成長すると予測している。 SiCはウエハー品質が課題、GaNは統合がトレンドに

SiCはウエハー品質が課題、GaNは統合がトレンドに

パワーエレクトロニクスは、GaN(窒化ガリウム)とSiC(炭化ケイ素)の採用によって、興味深い道を歩んできた。フランスの市場調査会社であるYole Developpement(以下、Yole)は、これらのワイドバンドギャップ材料の概観を発表した。 バーチャルブースで第4世代SiC-MOSFETなど展示

バーチャルブースで第4世代SiC-MOSFETなど展示

ロームは、オンライン開催となったパワーエレクトロニクス展示会「PCIM Europe digital days 2020」(2020年7月7〜8日、ドイツ時間)に出展。バーチャルブースを用意し、第4世代SiC-MOSFETなどの製品を紹介していた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- わずか3個のLSIでモバイル超音波診断装置を実現、ソシオネクスト

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」