銅(Cu)配線の微細化と抵抗値の増大:福田昭のデバイス通信(282) Intelが語るオンチップの多層配線技術(3)

引き続き、オンチップの多層配線技術に関するIntelの講演内容を紹介する。今回は、銅配線の寸法と電気抵抗の関係を説明する。

銅(Cu)配線の寸法と電気抵抗の関係

半導体のデバイス技術と回路技術に関する国際学会「VLSIシンポジウム」では、「ショートコース(Short Course)」と呼ぶ技術講座を開催してきた。2020年6月に開催されたVLSIシンポジウムのショートコースは、3つの共通テーマによる1日がかりの技術講座が設けられていた。3つの共通テーマとは、「SC1:Future of Scaling for Logic and Memory(ロジックとメモリのスケーリングの将来)」「SC2:Heterogeneous Integration - To Boldly Go Where No Moore Has Gone Before(ヘテロ集積化-果敢に進め、ムーアが行ったことのない場所へ)」「SC3:Trends and Advancements in Circuit Design(回路設計の動向と進化)」である。蛇足だが、SC2のタイトルは、SF映画「スター・トレック」の有名なフレーズ「to boldly go where no one has gone before(誰も行ったことのない場所へ果敢に進め)」のオマージュだろう。

話題を戻そう。共通テーマ「ロジックとメモリのスケーリングの将来」では、「On-Die Interconnect Challenges and Opportunities for Future Technology Nodes(将来の技術ノードに向けたオンダイ相互接続の課題と機会)」と題する講演が非常に興味深かかった。そこで、講演の概要を前々回からシリーズでお届けしている。講演者はIntelのMauro J. Kobrinsky氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前々回では、講演のアウトライン(目次)や配線技術の動向などを述べた。前回では、ムーアの法則と配線技術の関わりを解説した。今回は、代表的な金属配線である「銅(Cu)配線」の寸法と電気抵抗(単位長当たりの抵抗値)の関係を説明する。

単純に微細化すると1世代で配線抵抗は2倍に上昇

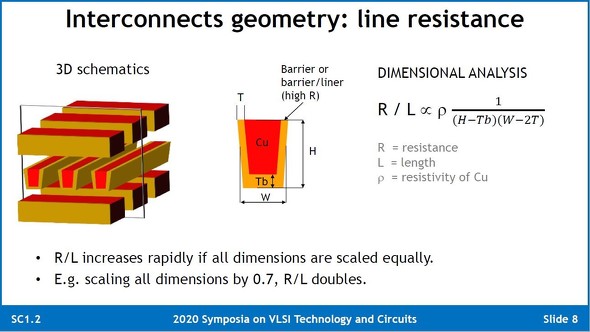

大規模ロジックにおける銅(Cu)金属の多層配線は、各層の配線が平行に並んでおり、なおかつ上下の配線層とは直交するようにレイアウトすることが多い。配線自体は、銅(Cu)金属配線と絶縁膜の境界を「バリア(barrier)層」および「ライナー(liner)層」と呼ぶ別の合金で囲んでいる。バリア層はCu金属原子が配線から周囲の絶縁膜へと拡散するのを防ぐ。ライナー層は、Cu配線を電解メッキで成膜するときの出発面となる極めて薄いCu膜をCVD(化学的気相成長)で均一に成長させるように働く。

バリア層とライナー層には、いずれも銅(Cu)に比べて抵抗率が高い金属材料を使う。従ってバリア層とライナー層は、配線抵抗を増加させる。

微細化によって製造技術のノードを1世代進めるとき、一般的には寸法を0.7倍に縮小する。例えば、金属配線で寸法を0.7倍に縮小すると、配線抵抗の値(配線長当たりの抵抗値)は2倍に上昇してしまう。実際にはこのような寸法の縮小は許されない。配線の幅(ピッチ)はある程度まで短くするものの、配線の高さはあまり低くならない。すなわち配線のアスペクト比(高さ/幅)が上がり、断面の形状は縦長になる。

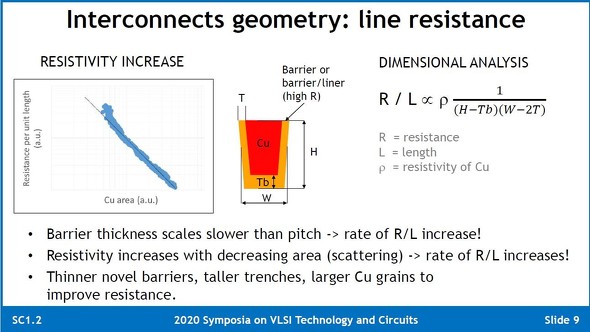

配線ピッチを縮小してもバリア層を薄くできない

配線ピッチを縮小するときには、バリア層の厚みも縮小することが望ましい。しかしバリア層をあまり薄くすると、Cu原子の拡散を防げなくなる。ある程度までしか、バリア層は薄くできない。

すなわち微細化を進めると、ある段階から配線断面に占めるバリア層の比率が上昇する。バリア層の金属は通常、Cuよりも抵抗率が高い。このため、微細化によって抵抗値が急速に増大する。

そこで対策として、より薄くできる新たなバリア金属の探索、配線高さのかさ上げ、Cu結晶粒(グレイン)の寸法拡大による抵抗率の低減、などが試みられている。

(次回に続く)

⇒「福田昭のデバイス通信」連載バックナンバー一覧

関連記事

ムーア則の維持に貢献する配線技術

ムーア則の維持に貢献する配線技術

「VLSIシンポジウム」から、オンチップの多層配線技術に関するIntelの講演内容を紹介するシリーズ。将来の配線技術には、サブトラクティブ法や低誘電率絶縁材料などに期待がかかっている。 接合材料に対する要求項目のランキング

接合材料に対する要求項目のランキング

ロードマップ第6章「実装設備」の第4節「実装技術動向」を説明するシリーズ。今回は、「接合材料」に対するユーザーの要望を調査した結果を紹介する。 実装設備が対応すべきプリント配線板と部品供給方式のロードマップ

実装設備が対応すべきプリント配線板と部品供給方式のロードマップ

引き続き、「実装技術動向」を紹介する。今回は、実装設備が対応すべき、プリント配線板と部品供給方式のロードマップについて解説する。 ベアチップ/フリップチップを高い精度で装着

ベアチップ/フリップチップを高い精度で装着

実装設備に要求する項目のアンケート結果を紹介するシリーズ。今回は「ベアチップ/フリップチップボンダ」に対する要求を説明する。 重要さを増す検査機からのフィードバック

重要さを増す検査機からのフィードバック

引き続き、実装設備に要求する項目のアンケート結果を紹介する。今回は、「検査機」に対する要求と対策を取り上げる。 高速・高精度・低コストの実装工程を支える設備と材料

高速・高精度・低コストの実装工程を支える設備と材料

第6章「実装設備」の概要を説明する。まずは表面実装の設備と材料を取り上げる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- 全固体ナトリウム電池の量産化に向けた新合成プロセスを開発、大阪公立大

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」