エプソンがDMOS-ASICの外販事業を開始:高耐圧、大電流の用途に向け

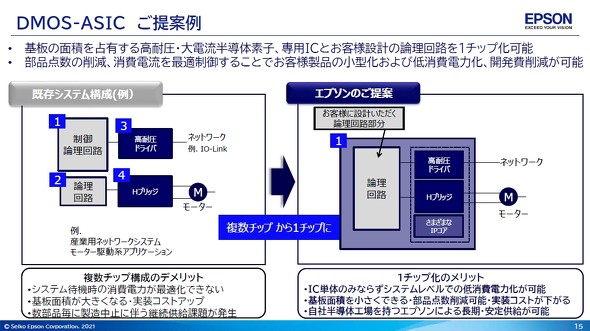

セイコーエプソン(以下、エプソン)は2021年5月26日、高耐圧、大電流のDMOS-ASICを外販する事業を開始したと発表した。DMOSにIP(Intellectual Property)コアと論理回路を混載して1チップ化したもので、第1弾として「S1X8H000/S1K8H000シリーズ」を開発。国内での受注を開始する。

内需で蓄積したノウハウを外販に生かす

セイコーエプソン(以下、エプソン)は2021年5月26日、高耐圧、大電流のDMOS-ASICを外販する事業を開始したと発表した。DMOSにIP(Intellectual Property)コアと論理回路を混載して1チップ化したもので、第1弾として「S1X8H000/S1K8H000シリーズ」を開発。国内での受注を開始する。IO-Linkなどの通信送受信回路、高電圧スイッチ、スイッチング電源、モーター駆動系といった幅広い分野の用途に向ける。

もともとエプソンは約50年前から、時計向けの半導体デバイスを手掛けてきた。時計用のため、基本的には高精度ながら小型で省電力(同社は「省・小・精」と呼ぶ)のCMOS IC(ASIC)の開発が主要だったが、近年は、時計だけでなくプリンタやプロジェクター、ロボットといった新しいアプリケーションも手掛けるようになっており、より大電力、高電圧なASICへの要望が社内であった。そうした背景から、エプソンは内需(社内での需要)向けに、高耐圧、大電流を実現できるDMOS ICを数多く開発してきた。

エプソンが内製で提供してきた半導体デバイスおよびアプリケーションの例。CMOSだけでなくDMOSプロセスも用いたさまざまな半導体デバイスが、完成品を通じて顧客に提供されてきた。ウエハー製造(前工程)は山形県酒田市の自社工場で行っている 出典:エプソン(クリックで拡大)

エプソンが内製で提供してきた半導体デバイスおよびアプリケーションの例。CMOSだけでなくDMOSプロセスも用いたさまざまな半導体デバイスが、完成品を通じて顧客に提供されてきた。ウエハー製造(前工程)は山形県酒田市の自社工場で行っている 出典:エプソン(クリックで拡大)今回のDMOS-ASIC外販事業は、そこで培ってきた技術を活用する。エプソンのデバイスプロダクトマーケティンググループで課長を務める徳永泰之氏は、「これまで外部に販売してきた半導体デバイスは、低電圧/低消費電力の製品だったが、DMOS-ASICはその対極となる高耐圧、大電流という位置付けになる。長年、完成品を通じて提供してきたASIC、つまり低パワーのロジックICと、社内で脈々と培ってきた、大電流を得意とするDMOSプロセスを組み合わせる」と説明する。

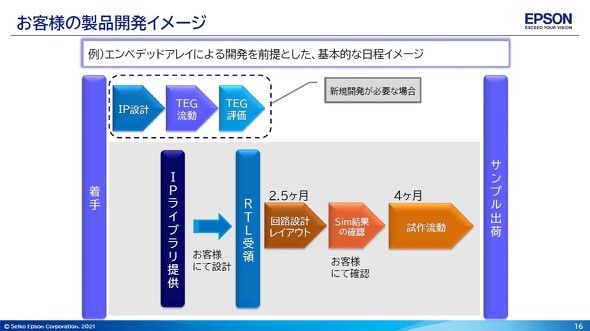

エプソンのASICは、回路の集積度が異なる「ゲートアレイ」「エンベデッドアレイ」「スタンダードセル」の3つを提供している。電源と信号配置を自由に設定できるゲートアレイ、ASSPなどの特定用途向けハードマクロを搭載し、顧客の回路をSOG(Sea Of Gate)で実現して混載できるセミカスタムのエンベデッドアレイ、最適設計されたロジックセルとROM/RAM、CPU周辺、アナログ回路などを1チップ化できるセミカスタムのスタンダードセルとなっており、スタンダードセルの回路の集積度が最も高い。第1弾として発表したS1X8H000/S1K8H000シリーズでは、S1X8H000のASICがエンベデッドアレイ、S1K8H000のASICがスタンダードセルとなっている。

左=新製品のDMOS-ASICの位置付け。なお、既存のASICシリーズ(灰色で表示されているシリーズ)は、いずれもDMOSではなくCMOSを採用している/右=S1X8H000/S1K8H000シリーズの仕様 出典:エプソン(クリックで拡大)

左=新製品のDMOS-ASICの位置付け。なお、既存のASICシリーズ(灰色で表示されているシリーズ)は、いずれもDMOSではなくCMOSを採用している/右=S1X8H000/S1K8H000シリーズの仕様 出典:エプソン(クリックで拡大)S1X8H000/S1K8H000シリーズは0.15μmのCMOS/DMOS混載プロセスで、エプソン独自の回路化技術により、アナログ系制御素子の集積を可能にしている。エプソンが提供する高耐圧、大電流の電源ICやさまざまなIPコアと、顧客が設計する論理回路を、DMOS-ASICとして1チップ化する。

IPコアは、過電流検知機能付きDMOSトランジスタやHブリッジ回路、LDO(低ドロップアウト)レギュレーター回路、EEPROM、SRAM、過電圧や過熱検知などを、順次開発していく予定だ。

徳永氏は、「これまでは電源ICと論理回路(ASIC)を1チップに混載できなかったので、これまでは顧客が、それぞれのICを別々に基板上に実装して評価していた。今回は、高耐圧のDMOSと低電圧のCMOSを1チップ化することで、基板上の部品点数の削減や、(チップの数が減るので)低消費電力化や小型化、開発費の削減といったメリットが得られる」と説明する。

必要なICを購入してきてシステムを構成する既存の方法には、リスクも伴う。「昨今、半導体不足が問題となっているが、例えば電源ICが不足したり、ICがディスコン(生産中止)になったりするケースがある他、発熱やサイズなどの課題も発生する。今回発表したDMOS-ASICは、必要な機能を1チップ化できるので、そうした問題を気にすることなく最適なカスタムICを開発できる。さらに、自社工場で製造しているので、長期的に安定した供給が可能なこともメリットだ」(徳永氏)

関連記事

16階調のセグメント表示が可能な液晶ドライバーIC

16階調のセグメント表示が可能な液晶ドライバーIC

セイコーエプソンは2021年2月25日、車載ディスプレイシステム向けにセグメント液晶ドライバーIC「S1D15106」を開発し、量産したと発表した。 クレカを守る、EPDドライバー内蔵16ビットマイコン

クレカを守る、EPDドライバー内蔵16ビットマイコン

セイコーエプソンは2019年10月16日、小型の電子ペーパーディスプレイ(EPD)を駆動するドライバーを搭載した16ビットマイコン「S1C17F63」を開発したと発表した。サンプル出荷は既に開始していて、サンプル価格は、パッケージタイプがQFP15-100のもので650円(税別)。量産は2019年内に開始する予定だ。 半導体不足、解消の鍵は「300mmウエハーへの移行」

半導体不足、解消の鍵は「300mmウエハーへの移行」

8インチ(200mm)ウエハーのサプライチェーンは、控えめに言っても、かなり厳しい状況にある。これは、決して新しい問題ではない。台湾の市場調査会社TrendForceが2020年11月に発表したプレスリリースでは、「8インチウエハーの生産能力に関しては、2019年後半から深刻な不足状態が続いている」と述べている。 IBMが「2nm」プロセスのナノシートトランジスタを公開

IBMが「2nm」プロセスのナノシートトランジスタを公開

IBMは、米国ニューヨーク州アルバニーにある研究開発施設で製造した「世界初」(同社)となる2nmプロセスを適用したチップを発表した。同チップは、IBMのナノシート技術で構築したGAA(Gate-All-Around)トランジスタを搭載している。 原子層エッチングがEUVの確率変動を低減

原子層エッチングがEUVの確率変動を低減

次世代の半導体製造プロセスに必須ともいわれるEUV(極端紫外線)リソグラフィ技術。今回は、大手装置メーカーのLam Researchが、EUVリソグラフィにおいて重要な要素となる確率変動について解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- Raspberry PiがAIカメラモジュール発売へ、ソニーのAI処理機能搭載センサー採用

- 「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?

- ルネサス甲府工場がいよいよ再稼働 柴田社長「パワー半導体の戦略的拠点に」

- 就業人員の4割が帰還組、ルネサス甲府工場が10年の時を経て再稼働

- 2024年はDRAM/NAND市場が回復へ 需給バランスも正常化

- 日本伝統の「和装柄」がヒントに 半導体の高度な熱管理につながる技術

- 信越化学が国内に新生産拠点、半導体露光材料事業の拡大に向け

- 受託開発の内容を「メニュー」としてサービス化、日立が本格展開

- 半導体製造装置の販売額、2023年は1063億ドルで前年比1.3%減

- MicrochipがTSMCとの提携を拡大、JASMを通じて40nm特化の生産能力を確保