楢嵹

10nm偱嬯愴偡傞Intel丄栤戣偼Co攝慄偲Ru僶儕傾儊僞儖偐丗搾擵忋棽偺僫僲僼僅乕僇僗乮9乯乮2/5 儁乕僕乯

Intel偼2016擭埲崀丄崱擔偵帄傞傑偱丄10nm僾儘僙僗傪棫偪忋偘傞偙偲偑偱偒偰偄側偄丅堦曽偱丄攝慄僺僢僠偼摨摍偱偁傞偼偢偺丄TSMC偲Samsung Electronics偺7nm僾儘僙僗偼寁夋捠傝偵恑傫偱偄傞丅偱偼側偤丄Intel偼10nm僾儘僙僗偺棫偪忋偘偵嬯愴偟偰偄傞偺偩傠偆偐丅

Intel偺10nm僾儘僙僗偲偼

丂Intel偼2017擭12寧丄僒儞僼儔儞僔僗僐偱奐嵜偝傟偨敿摫懱偺崙嵺妛夛乽IEDM乿偱丄乬A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects乭偺僞僀僩儖偱敪昞偟丄悽奅偱弶傔偰僐僶儖僩乮Co乯攝慄傪巊偭偨偙偲傪柧傜偐偵偟偨丅

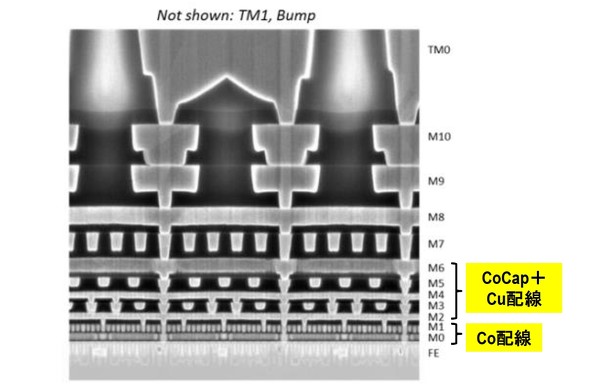

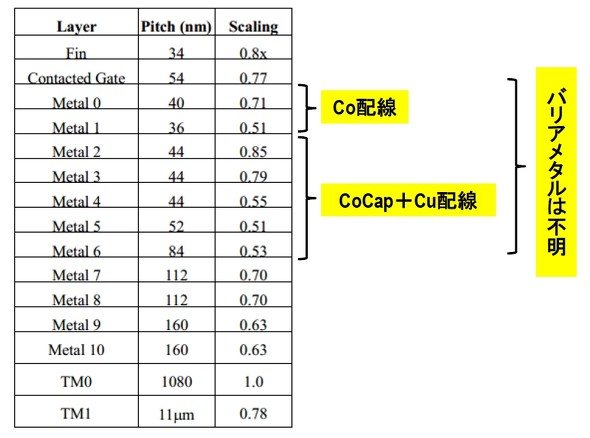

丂昅幰偼丄2016擭崰偐傜丄旝嵶攝慄偺嵽椏偑Cu偐傜Co丄Ru乮儖僥僯僂儉乯丄Mn乮儅儞僈儞乯側偳偵曄傢傞偐傕偟傟側偄挍岓傪偮偐傫偱偄偨丅廬偭偰丄偙偺榑暥偱Intel偑Co攝慄傪巊偭偨偙偲偵拲栚偟偨丅Intel偺忋婰榑暥偵傛傟偽丄M0偲M1偵Co攝慄傪巊梡偟丄M2乣M6偺攝慄偵偼Cu攝慄偲Co僉儍僢僾傪巊偭偨偲彂偐傟偰偄傞乮恾1丄恾2乯丅偟偐偟丄僶儕傾儊僞儖嵽椏偵偮偄偰偺婰嵹偼側偄丅

丂偙偙偱丄懡憌攝慄偺峔憿偑丄僶儖僋攝慄嵽椏丄僶儕傾儊僞儖丄僉儍僢僾偐傜峔惉偝傟偰偄傞偙偲傪愢柧偟偨忋偱丄側偤丄Cu偐傜Co側偳偵攝慄嵽椏偑曄峏偝傟側偔偰偼側傜側偄偺偐傪徻弎偡傞丅

Copyright © ITmedia, Inc. All Rights Reserved.