10mWでジェスチャー検出、超小型FPGAを使うエッジAI:CEATEC 2019

Lattice Semiconductor(以下、Lattice)は「CEATEC 2019」(2019年10月15〜18日、幕張メッセ)で、エッジ端末において低消費電力で推論する技術のデモを展示した。

Lattice Semiconductor(以下、Lattice)は「CEATEC 2019」(2019年10月15〜18日、幕張メッセ)で、エッジ端末において低消費電力で推論する技術のデモを展示した。

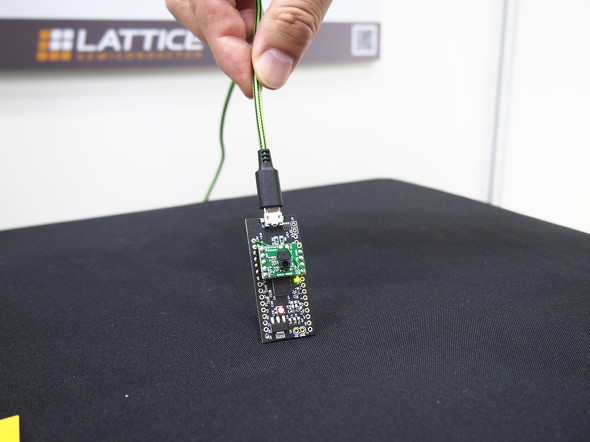

まずは、Latticeの超小型FPGAである「iCE40 UltraPlus」と赤外線センサーを使ったハンドジェスチャー検出のデモを紹介する。赤外線センサーで手の形を大まかに判断し、そこからグー・チョキ・パーを判断するもので、消費電力は10mW以下だという。Latticeの説明担当者は、「『iCE40クラスの超小型FPGAには、推論アルゴリズムを実装できないと思っていた』と驚かれることが多い」と話す。「このレベルの低消費電力かつ小型だと、できる処理量は限られるが、それでもいいと割り切ればここまでできるということを示したかった」(同氏)

小型のFPGA「iCE40 UltraPlus」と赤外線センサーを搭載したデモ用のボード。指の大きさと比べると、かなり小型なのが分かるが、グー・チョキ・パーの判断はしっかりできていた(クリックで拡大)

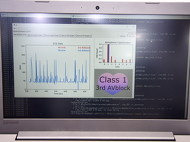

さらに、「Lattice sensAIスタック」を用いて開発した心電図異常検知システムのデモも行った。Lattice sensAIスタックは、iCE40 UltraPlusなどを搭載したレファレンスボードと、CNN(畳み込みニューラルネットワーク)アクセラレーターのIP(Intellectual Property)コア、ニューラルネットワークコンパイラ、顔検出やハンドジェスチャー検出といったレファレンスデザインで構成されている。

心電図異常検知システムのデモは、Lattice sensAIの認定パートナー企業であるポコアポコネットワークスが開発したものだ。一般公開されている心電図の医療波形データで学習させ、16ビットの量子化CNNにより波形異常を検知している。

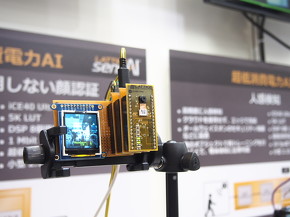

iCE40 UltraPlusを2個使用し、クラウドを使わない顔認証のデモも展示した。FPGAを2個使い、規模が少し大きいニューラルネットワークを使えるようにしている。顔の特徴点を128カ所見つけ出して、顔認証を行う。「クラウドが不要なので、コストを抑えられる上に、ネットワーク接続の異常といった不具合も避けることができる」(Lattice)

関連記事

超小型FPGAをエッジに、独自路線を進むLattice

超小型FPGAをエッジに、独自路線を進むLattice

小型で低消費電力のFPGAを手掛けるLattice Semiconductorは、クラウド市場に注力する他のFPGAベンダーとは明確に路線を分け、エッジ向けに力を入れる。 FPGA大手で唯一生き残るXilinx、国内戦略を聞く

FPGA大手で唯一生き残るXilinx、国内戦略を聞く

FPGA大手ベンダーで唯一買収されずに生き残っているXilinx。同社日本法人のザイリンクス社長で韓国のVice Presidentを務めるSam Rogan(サム・ローガン)氏に国内の戦略を聞いた。 エッジAIこそ日本の“腕の見せどころ”、クラウドとの連携も鍵

エッジAIこそ日本の“腕の見せどころ”、クラウドとの連携も鍵

今回は、業界で期待が高まっている「エッジコンピューティング」を解説する。AWS(Amazon Web Service)やMicrosoft、半導体ベンダー各社も、このトレンドに注目し、取り組みを加速している。 AIはFPGAのスイートスポット、Xilinxがエッジ推論をデモ

AIはFPGAのスイートスポット、Xilinxがエッジ推論をデモ

Xilinxは、組み込み技術の国際展示会「embedded world 2019」(2019年2月26〜28日、ドイツ・ニュルンベルク)で、自動車や監視カメラなどでの推論、いわゆるエッジデバイスでの推論をイメージしたデモを展示した。 エッジAIを安価・高速に、FPGAを駆使するベンチャー

エッジAIを安価・高速に、FPGAを駆使するベンチャー

LeapMindは2018年8月31日、東京都内で同社初となるプライベートカンファレンス「DeLTA TECH 2018」を開催した。このイベントでは、LeapMindの強みとなる技術が多く明かされていた。 Microchip、AI機能搭載のエッジ機器開発を支援

Microchip、AI機能搭載のエッジ機器開発を支援

Microchip Technologyは、子会社のSilicon Storage Technology(SST)を介し、電池駆動のエッジデバイスにAI推論機能を搭載するための支援を行う。

Copyright © ITmedia, Inc. All Rights Reserved.