ARMから見た7nm CMOS時代のCPU設計(12)~トランジスタ構造の展望:福田昭のデバイス通信(23)(1/2 ページ)

今回は、トランジスタ構造の展望を、2つの軸に沿って見ていこう。1つ目はプレーナFETからFinFETへの移行、2つ目は14nm世代から5nm世代にかけてのトランジスタ仕様である。FinFETの登場は、プレーナFETにはなかった新たな課題をもたらしている。

プレーナFETからFinFETへの移行

MOSトランジスタの構造は、22nm世代から16nm/14nm世代にかけて大きく変わろうとしている。従来のMOSFET(プレーナMOSFET)を、FinFET(フィンフェット)で置き換える。

FinFETとプレーナFETの構造的な違いは、「フィン」の存在だろう。FinFETでは、シリコンウエハー表面に対して垂直に薄い板状のシリコン(フィン)が存在する。フィンはMOSトランジスタのソースとドレイン、チャンネルの領域となる。フィンの中央には、フィンを横切るように細長いゲート電極が載る。

FinFETは、基本的にはフィンの側壁がゲートとなる。つまりゲートが2つある、ダブルゲートのトランジスタである。ゲートが2つあるので、シングルゲートである従来のプレーナFETに比べると制御性が大幅に向上する。またフィンが薄いのでチャンネル部分は完全に空乏化する。チャンネル部分への不純物ドーピング濃度はプレーナFETに比べると低くなり、高濃度ドーピングの問題点であるしきい電圧のばらつきが減少するという利点が生じる。一方で、フィンの寸法、特に厚みの均一性に対する要求は非常に厳しくなる。これには、フィン1個の側壁が平らにならない問題と、膨大な数のフィンで厚みがばらつく問題の2つがある。いずれもプレーナFETでは存在しなかった、新しい課題だ。

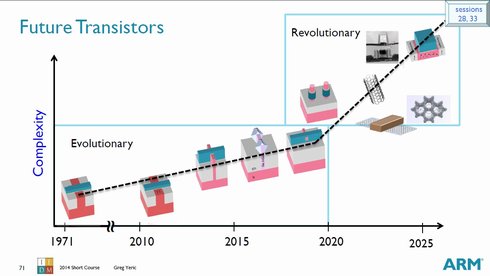

2010年から2025年にかけてのトランジスタ構造の展望。1970年代から2010年代前半まではプレーナMOSFETの時代が続いた。2010年代半ばにはトランジスタ構造の変更が始まる。まずFinFETが登場する(グラフの左から3番目)。FinFETの時代は長くは続かない。長くても3世代程度といわれている(クリックで拡大) 出典:ARM

2010年から2025年にかけてのトランジスタ構造の展望。1970年代から2010年代前半まではプレーナMOSFETの時代が続いた。2010年代半ばにはトランジスタ構造の変更が始まる。まずFinFETが登場する(グラフの左から3番目)。FinFETの時代は長くは続かない。長くても3世代程度といわれている(クリックで拡大) 出典:ARM14nm世代から5nm世代までのトランジスタ仕様

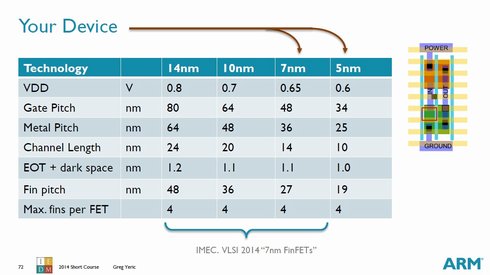

ARMは講演で、14nm世代から5nm世代までのトランジスタ仕様を展望してみせた。具体的には、14nm世代、10nm世代、7nm世代、5nm世代に分けて示した。トランジスタ構造としては、いずれもFinFETを仮定し、トランジスタ当たりのフィンの枚数は最大で4枚とした。

仕様の詳細を見ていこう。最初は電源電圧である。14nm世代の0.8Vから、10nm世代の0.7V、7nm世代の0.65V、5nm世代の0.5Vと、ゆっくりと低下していく。言い換えると、電源電圧を下げる余地はほとんど残っていない。

続いてゲートピッチとメタルピッチである。14nm世代では80nmのゲートピッチがあった。それが7nm世代では48nmとなり、5nm世代では34nmと大幅に短くなる。メタルピッチはさらにアグレッシブだ。14nm世代でのメタルピッチは64nm。これが7nm世代では36nmとなる。5nm世代では25nmである。

フィンのピッチはさらに厳しい。14nm世代でのフィンピッチは48nm。メタルピッチよりも短い。7nm世代ではフィンピッチは27nm、5nm世代に至っては19nmとなる。これらのピッチを従来の微細加工技術の改良で、実用的なコストで製造できるかは、まだ分からない。

一方でゲート絶縁膜の厚さは既に、薄さの限界に達している。酸化膜厚換算で14nm世代は1.2nmである。10nm世代と7nm世代はともに1.1nm、5nm世代でも1.0nmとほとんど変わらない。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- 「LiDARより高精度で低コスト」ソニーのエッジAI、スマート都市で真価

- まるでボタン、でも平ら リアルさを追求する京セラのハプティクス技術

- 高解像度で高精度のダイレクト露光装置を開発、25年度内に製品化

- 前工程装置でシェア低下が続く日本勢、気を吐くキヤノンは希望となるか

- 米国政府がIntel株を10%取得 元王者の救済は「国有化への序章」か?

- 「富岳NEXT」開発が始動 GPUでNVIDIA参画、Rapidus採用の可能性も

- シャープが亀山北工場を売却 12億円で

- NVIDIAとAMDが米政府に中国売上高の15%を支払い、影響は

- 25年2Qの半導体企業ランキング、日本勢トップは13位のソニー

- 2025年上半期の半導体業界を振り返る