「ムーアの法則」継続の鍵となるか、Si/III-V族の“ハイブリッド”ナノワイヤ:プロセス技術(1/2 ページ)

IBM研究所が、Si(シリコン)とIII-V族化合物半導体を組み合わせたナノワイヤを形成する技術を発表した。独自の「TASE(Template-Assisted Selective Epitaxy)」という技術を使って形成する。TASEで作成したInAs(インジウムヒ素)のナノワイヤは、5400cm2/Vsの電子移動度を達成したという。「ムーアの法則」を継続させる鍵になるかもしれない。

「ムーアの法則」が再び勢いづく可能性がある。SOI(シリコン・オン・インシュレータ)基板のトランジスタチャネルなどに適した、III-V族化合物半導体ナノワイヤの形成が鍵になりそうだ。スイスのチューリッヒと米国ニューヨーク州ヨークタウンハイツに拠点を置くIBM Researchが発表した。

IBMは、独自の「TASE(Template-Assisted Selective Epitaxy)」と呼ばれる技術を用いて、ナノスケールのホール構造やマルチゲートFET(MuG-FET)を製造したという。

IBMの2つの研究拠点が協力したこの取り組みは、Intelを含め、世界中の半導体メーカーが長年開発してきたことを実現したようだ。

IBMは、Applied Physics Lettersで発表した論文の中で、Si(シリコン)とIII-V族化合物半導体*)間の結晶格子の不整合を取り除く技術や、TASEの開発における初期段階の取り組みなどを引用している。結晶格子の不整合を取り除く技術は、他の研究機関が一部、成功しているものだ。

*)InAs(インジウムヒ素)、InGaAs(インジウムガリウムヒ素)、GaAs(ガリウムヒ素)

ナノワイヤ形成のステップ

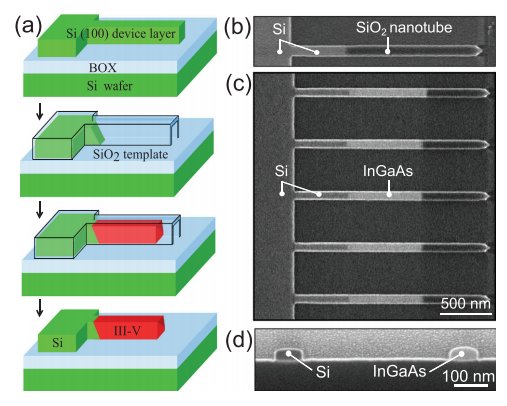

TASEによるナノワイヤ形成のステップは、以下の図の(a)に示されている。

まず、SOI基板上に、Siでナノワイヤを形成する。その上に、SiO2層をALD(原子層堆積)で形成。このSiO2層の中に残っているSiナノワイヤの端をエッチングで切り取る。ここに、III-V族化合物半導体の結晶を、有機金属気相成長法を用いて成長させる。最後に、SiO2層を除去する。そうすると、一番下のように、SiとIII-V化合物半導体を組み合わせたナノワイヤができる。(b)~(d)は、作成したナノワイヤの電子顕微鏡写真だ。

Copyright © ITmedia, Inc. All Rights Reserved.

- EE Times Japanテ勇DN Japan 邨ア蜷磯崕蟄千沿�唔oT繧サ繧ュ繝・繝ェ繝�ぅ縺ョ迴セ蝨ィ蝨ー窶補暮崕蟄千沿2025蟷エ10譛亥捷

- EMI菴取ク帙r蜿ッ閭ス縺ォ縲�4繧ケ繧、繝�メ縺ョ繧ウ繝ウ繝医Ο繝シ繝ゥ繝シ繧呈治逕ィ縺励◆髮サ貅占」ス蜩√→縺ッ��

- AI繝サEV繝サ5G譎ゆサ」縺ォ蟇セ蠢懊�崕貅占ィュ險医�譁ー縺溘↑繧「繝励Ο繝シ繝√→縺ッ��

- 謖∫カ壼庄閭ス諤ァ縺ォ驟肴�縺励◆谺。荳紋サ」繧「繝励Μ繧ア繝シ繧キ繝ァ繝ウ逕ィ繝「繝シ繧ソ繝シ繝サ繧ィ繝ウ繧ウ繝シ繝繝シ縺ョ險ュ險�

- 繧、繝ウ繝�Μ繧ク繧ァ繝ウ繝医�繝弱�繝峨r驕�髫泌宛蠕。縺吶k謚陦薙〒縲∽ソ。鬆シ諤ァ縺ョ鬮倥>閾ェ蜍募喧繧貞ョ溽樟縺吶k

記事ランキング

- 半導体不足で自動車業界が再び混乱か、オランダ政府によるNexperia接収の衝撃

- 村田製作所、25年Q2は過去最高の売上高に AI需要でMLCC好調

- SCREENがニコンのウエハー接合技術を譲受 先端パッケージ領域の成長図る

- 家庭用人型ロボットに驚き 日本はまた「早過ぎた」のか

- ルネサス、25年通期は減収予想 開発基盤「Renesas 365」は年内ローンチへ

- onsemiが縦型GaNパワー半導体開発、700Vと1200V品をサンプル提供

- ソシオネクストが通期利益を下方修正、25年2Qは増収減益

- HDD大手Seagateの四半期業績は増収増益、営業利益率は30%に近づく

- 24年のGaNデバイス市場、シェア1位は中国 トップ5に日本勢なし

- Intel、SambaNova買収へ交渉中か AI推論分野での追い上げ目指す

「TASE」によるSi/III-Vナノワイヤ 出典:IBM Researchの論文

「TASE」によるSi/III-Vナノワイヤ 出典:IBM Researchの論文