キャッシュメモリの基礎:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(6)(1/3 ページ)

今回は、キャッシュメモリについて解説する。キャッシュの考え方はとてもシンプルだが、実装となるとさまざまな方法があって複雑だ。今回は、3つのキャッシュアクセス構造について説明しよう。

キャッシュとは何か

国際会議「IEDM」のショートコースで英国ARM Reserch社のエンジニアRob Aitken氏が、「System Requirements for Memories(システムがメモリに要望する事柄)」と題して講演した内容を紹介するシリーズの第5回である。

前回は、CPUの基本的なアーキテクチャを説明した。またCPUの演算性能を向上させるさまざまな手段が、メモリ・システムを複雑にしていることを述べた。今回は、キャッシュメモリ(キャッシュ)の基礎に関する講演部分をご紹介する。

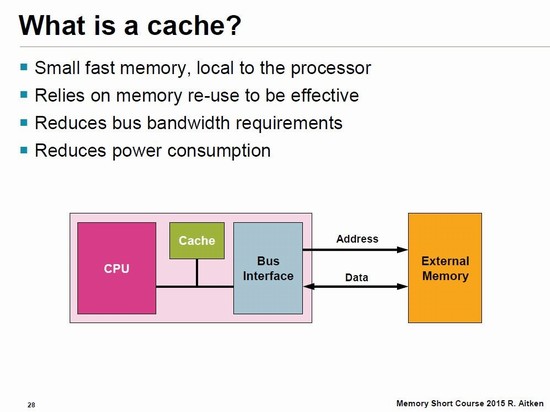

キャッシュとは本シリーズの第3回で既に説明したように、メモリ階層ではCPU(レジスタ)とシステム・メモリ(主記憶あるいはメインメモリとも呼ぶ)の間に存在し、システム・メモリの内容のごく一部を一時的に保存しておくメモリである。キャッシュはシステム・メモリに比べるとはるかに高速で、その代わりに記憶容量が小さい。

キャッシュに保存するのは、CPUが頻繁にアクセスすると予想される命令や数値(データ)などである。キャッシュによって低速なシステム・メモリへのアクセス頻度を最大限度まで減らし、CPUの平均的な待ち時間を短縮することによって実効的な演算性能を高める。

キャッシュには、CPUとシステム・メモリを接続するバス(メモリバス)のデータ転送速度に対する要求値を下げるという働きもある。これはコスト低減と消費電力低減の両方に効く。

キャッシュの基本的な用語

キャッシュの基本的な考え方は非常に分かりやすい。しかし、その実装方法は多様で複雑であり、あまり分かりやすいとはいえない。キャッシュ技術に関する用語だけでも、標準的なメモリの世界とは随分と違っている。ここでは基本的な用語にしぼって解説しておくことにする。

まず、キャッシュに格納するデータの大きさの単位を決める必要がある。この大きさの単位を「ライン(Line)」と呼ぶ。ラインの大きさ(長さ)は、16バイトから256バイトくらい。キャッシュの容量が大きなときは、ラインも大きくしやすい。

それから、キャッシュに格納したデータのアドレスもキャッシュに格納する必要がある。このアドレスを「タグ(Tag)」と呼ぶ。といってもラインの大きさで決まる下位ビットのアドレス(例えば64バイトのラインだと下位6ビット)はタグにする意味がないので、必要な上位ビットのアドレス(上位アドレス)だけをタグとする。

当然ながら、ラインの本数は1本ではない。例えば容量16Kバイトのキャッシュでラインのサイズが32バイトだとすると、ラインの本数は512本となる。このラインの集まりを、「セット(Set)」と呼ぶ。セットの数がいくつになるかは、ラインの本数とキャッシュアクセスの構造によって決まる。

キャッシュアクセスの構造に関連する基本用語が、「ウエイ(Way)」と「インデックス(Index)」である。これらの用語の説明は後述する。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

- 25年5月の世界半導体市場は全地域で成長、19.8%増の590億ドルに

- 危うい再建計画 Wolfspeed、CHIPS法補助金で再生図るか

- 半導体製造ラインの立ち上げ迅速に、日本IBMが京都に開発拠点

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- Qualcommの狙いは何なのか、やたらと「高い」Alphawave買収額

- 22nmプロセス採用でMRAM内蔵、ルネサスがエッジAI特化の新マイコン

- データセンター向けAI半導体のEsperantoが事業縮小、技術売却を模索

- 創刊前の20年間(1985年~2005年)で最も驚いたこと:「高温超伝導フィーバー」