キャッシュの基本動作:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(7)(1/3 ページ)

今回は、キャッシュメモリの基本動作について解説する。基本動作は、大きく分けて2つある。メインメモリからデータをキャッシュラインにコピーする「アロケーション」と、特定のキャッシュラインからデータを追い出して“空き”を作る「エビクション」だ。

1次キャッシュと2次キャッシュ、外部メモリの動作を見る

国際会議「IEDM」のショートコースで英国ARM Reserch社のエンジニアRob Aitken氏が、「System Requirements for Memories(システムがメモリに要望する事柄)」と題して講演した内容を紹介するシリーズの第5回である。

前回は、キャッシュメモリ(キャッシュ)の基礎に関する講演部分をご報告した。今回は、キャッシュの動作に関する講演の概要をご紹介する。

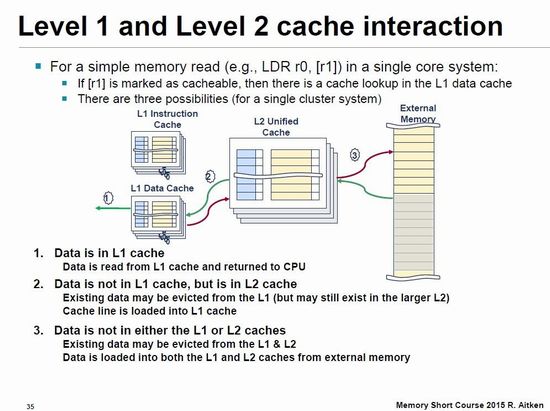

本シリーズの第3回で説明したように、キャッシュは複数のメモリ階層で構成されていることが多い。ここでは1次キャッシュ(命令キャッシュとデータキャッシュ)、2次キャッシュ(命令とデータを区別しないキャッシュ)、外部メモリ(CPUチップに外付するメモリ)の3つの階層によるメモリサブシステムを考える。記憶容量は1次キャッシュが最も小さく、次に2次キャッシュ(1次キャッシュの総容量よりも大きい)、最大が外部メモリとする。また複雑さを避けるために、CPUコアの数は1個(シングルコア)とする。

CPUがロード命令を出したと仮定しよう。アドレス[r1]のデータをレジスタr0に読み込む命令である。ここで、メモリ・アクセスに関して3通りのシナリオが考えられる。

(1)1次データキャッシュに対応するデータが存在する(1次データキャッシュにヒット):データキャッシュからデータを読み込み、CPUに戻す

(2)1次データキャッシュには対応データが存在せず、2次キャッシュに存在する(1次データキャッシュはミス、2次キャッシュはヒット):2次キャッシュのデータを読み込んでCPUに戻すとともに、1次データキャッシュにコピーする。1次データキャッシュのラインが全て埋まっていたときは、コピー前にどれかのラインからデータを追い出し、空きラインを作っておく

(3)1次キャッシュと2次キャッシュの両方ともに、対応するデータが存在しない(1次データキャッシュと2次キャッシュともにミス):外部メモリからデータを読み込み、CPUに戻すとともに、1次データキャッシュと2次キャッシュにデータをコピーする。このときもコピーの前に1次および2次キャッシュのラインに空きラインを作っておく

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 2

- PR -記事ランキング

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- 暗い夜道でも120m先の歩行者を検知、キヤノンが新SPADセンサー

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- 自律神経から「頑張りすぎ」を可視化、村田製作所

- 自動運転のキーデバイスとなる車載SoC

- キオクシアが攻める「NANDとDRAMのあいだ」 NVIDIAと協業も

- 次はデータセンター 「スマホ以外」にも手を広げるQualcomm

- 商用化から40年を迎えたFPGA、次の主戦場はエッジAI