欧州、III-V族半導体の開発プログラムを始動:約6億円を投じる3カ年計画

欧州が、III-V族化合物半導体の開発に本腰を入れる。IBMをはじめ、ドイツやフランスの研究機関、イギリスの大学など、欧州の知識を集結させて、III-V族半導体を用いたトランジスタの研究開発を進める。

およそ6億円を投じる一大プロジェクト

EU(欧州連合)は、470万ユーロ(約5億9000万円)を投じた3カ年プログラム「INSIGHT(Integration of III-V Nanowire Semiconductors for next Generation High performance CMOS SoC Technologies)」を始動した。INSIGHTの目標は、III-V族化合物半導体をチャンネル(以下、III-V族チャンネル)に採用したCMOSトランジスタを使って、次世代高性能SoCを実現することだ。5G(第5世代移動通信)や広帯域/高精細画像向けレーダーシステムへの活用を目指す。

INSIGHTには、スイスにあるIBMチューリッヒ研究所の他、ドイツFraunhofer IAF(フラウンホーファ応用固体物理学研究所)、フランスCEA-Leti(仏原子力庁の電子情報技術研究所)、スウェーデンLund University(ルンド大学)、イギリスUniversity of Glasgow(グラスゴー大学)、アイルランドのTyndall National Institute(ディンダル国立研究所)が参加している。

INSIGHTでは、IBMとLund University主導で、2つの方向から研究を進めている。IBMは、III-V族チャンネルで従来のプレーナ(平面)型トランジスタを試作している。一方、Lund Universityは、垂直のIII-V族チャンネルを用いたトランジスタの実現に向けた研究を行う。

IBMの科学者であるLukas Czornomaz氏は、EE Timesの独占インタビューに対して「INSIGHTでは、プレーナ型トランジスタと垂直トランジスタのどちらが有望かを見極めてから、RFテスト回路の作製に着手する計画だ。同プログラムが終了するまでに、RFパワーアンプ(PA)などの試作品を提供したい」と語った。

実績のある、IBMのIII-V族トランジスタ

IBMは、「プレーナ型トランジスタが採用されると確信している」という。同社は、2015年に発表した研究成果(参考)の中で、III-V族半導体を用いたトランジスタが14nm以下のプロセスでも実現できることを実証しているからだ。

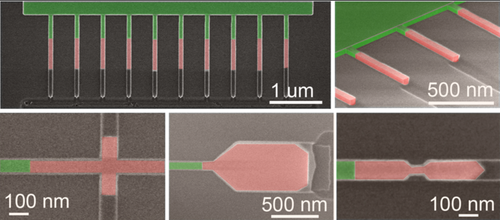

IBMは、「TASE(Template-Assisted Selective Epitaxy)*)」という手法を用いて、プレーナ型III-Vトランジスタを作製した。まず、空の酸化層を作り、そこにIII-V族チャンネルを形成することで、シリコン基板上にゲートファースト方式でCMOS互換III-V FinFETを作製するというものだ。

*)関連記事:「ムーアの法則」継続の鍵となるか、Si/III-V族の“ハイブリッド”ナノワイヤ

IBMは、III-V族チャンネルを用いたCMOSトランジスタを使うことで、既存よりも低い消費電力でミリ波帯無線通信が行えるとしている。5Gだけでなく、コグニティブコンピュータやIoT(モノのインターネット)の他、これらをサポートするクラウドベースのプラットフォームに適用できるとしている。

INSIGHTの目標は、全く新しい用途を実現する高性能SoCを、7nm以下のCMOSプロセスで作製することだ。INSIGHTは、全てのパートナーの専門知識を集結して、CMOSプロセスを適用したIII-V族半導体の開発に取り組んでいる。

【翻訳:滝本麻貴、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- あと5年で中国が半導体生産能力トップに 米国は先端ノード強化

- 中国はどうEVバッテリー市場を支配したか 欧米のミスは「固体電池への幻想」

- 「最古の銅酸化物」に微量の酸素をドープ、超伝導状態が発現

- 「標準化を待てず」 HBMで変わるメモリ技術サイクル

- DRAM市場でSK hynixが首位独走、Samsung引き離す 25年Q2

- シャープが亀山北工場を売却 12億円で

- 極薄の先端半導体チップを高スループットで実装、生産効率10倍

- 米国の中国向け装置輸出「特例撤回」 SamsungとSKへの影響は

- Samsungの半導体四半期業績、前期比で増収も利益率は1.4%に激減

- 高解像度で高精度のダイレクト露光装置を開発、25年度内に製品化

IBMの「TASE」を使って形成したIII-V族チャンネル 出典:IBM

IBMの「TASE」を使って形成したIII-V族チャンネル 出典:IBM Intelの10nmチップ、鍵はIII-V族半導体と量子井戸構造か

Intelの10nmチップ、鍵はIII-V族半導体と量子井戸構造か IBMが7nm試作チップを発表、Intelに迫る勢い

IBMが7nm試作チップを発表、Intelに迫る勢い 人間の脳が握る、デバイス低消費電力化の鍵

人間の脳が握る、デバイス低消費電力化の鍵 有機材料が“ムーアの法則”を延命する

有機材料が“ムーアの法則”を延命する