投機的プリフェッチとキャッシュの弱点:福田昭のデバイス通信 ARMが語る、最先端メモリに対する期待(8)(1/2 ページ)

今回は、メモリアクセスの高速化手法である「投機的プリフェッチ(Speculative Prefetch)」の仕組みを解説する。これは、“次のアクション”を推測して、データをキャッシュにコピーするものだ。この他、キャッシュが抱える本質的な弱点についても触れておきたい。

使われそうなデータをキャッシュにコピーしておく

国際会議「IEDM」のショートコースで英国ARM Reserch社のエンジニアRob Aitken氏が、「System Requirements for Memories(システムがメモリに要望する事柄)」と題して講演した内容を紹介するシリーズの第8回である。

前回で述べたように、キャッシュメモリ(キャッシュ)には、CPUがいったんアクセスしたデータを格納している。一度アクセスしたデータは、近い将来に再利用する可能性が高い(データの時間的局所性)。もう一度アクセスしたときはメインメモリではなくキャッシュラインにアクセスすることになるので、メモリアクセスの速度が大幅に高まる。

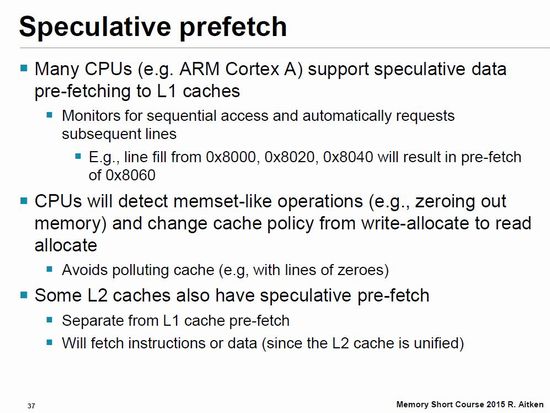

キャッシュと異なるメモリアクセスの高速化手法に「投機的プリフェッチ(Speculative Prefetch)」がある。まだアクセスしたことはないが、近い将来にアクセスすることがほぼ確実なデータを、あらかじめキャッシュに読み込んでおく。ARM Cortex Aシリーズをはじめとする多くのCPUが、1次データキャッシュに投機的プリフェッチ機能を搭載している。

例えば、キャッシュラインにアドレス「0x8000」、次に「0x8020」、さらには「0x8040」のデータをメインメモリからコピーしたとしよう。近い将来に、アドレス「0x8060」のデータにアクセスする可能性が高い。このようにハードウェアが判断し、CPUがアクセスする前のタイミングでキャッシュにコピーしておく。

またCPUは、memset関数のような動作(例えばメモリの値をゼロに設定する動作)を検出して、キャッシュのポリシー設定をライト・アロケーションからリード・アロケーションに変更する。ここでライト・アロケーションとは、リードあるいはライトの動作でキャッシュミスが発生したとき、キャッシュラインをメインメモリからのデータで満たすポリシーを意味する。

これに対してリード・アロケーションでは、リードのキャッシュミスが発生したときのみ、キャッシュラインを満たす。メモリにゼロを書き込む動作でポリシーがライト・アロケーションだと、キャッシュラインを汚染する(無効なデータで埋める)可能性が高い(ゼロ値は初期化だと推測できる)。そこでリード・アロケーションにポリシーを変更することで、キャッシュの汚染を防ぐ。

Copyright © ITmedia, Inc. All Rights Reserved.

スポンサーからのお知らせ

- PR -Special Contents 2

- PR -記事ランキング

- 世界半導体製造装置市場、2026年は過去最高に

- 2025年は数年に一度の「ビッグチェンジ」イヤー、NVIDIAとAMDの最新GPUを分解

- 「過去の投資は過剰だった」 Intel、ドイツとポーランドの新工場計画を中止

- ウシオ電機、オスラムグループのランプ事業を買収

- 車載SiCモジュール強化の三菱電機、独自モジュール「J3」の新製品投入へ

- 半導体業界 これまでの20年、これからの20年

- HBMと同等コストで記憶容量8倍、サンディスクが「HBF」推進強化

- 乾電池1本分の電圧で発光する白色有機ELを開発

- 村田製作所、25年1Qは減収減益 AIサーバ向け好調もスマホ向け需要減

- アオイ電子がシャープ三重第2工場も買収、先端半導体パッケージ強化