パワー半導体向け0.13μm技術、放電耐量を向上:静電気放電特性を改善、保護素子を32%に縮小

東芝は、アナログパワー半導体向け0.13μmプロセスを用いた静電気放電保護素子を開発した。従来の素子に比べて、静電気放電耐量は4倍に向上するとともに、放電耐量のばらつきを1/12に抑えることが可能となる。

静電気放電耐量は4倍、放電耐量ばらつき1/12

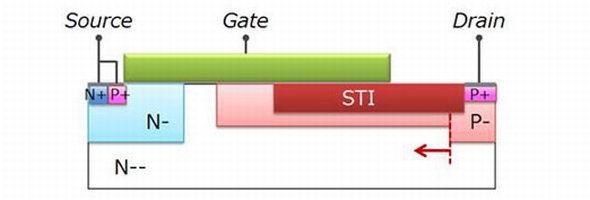

東芝は2016年6月、アナログパワー半導体向け0.13μmプロセスを用いた静電気放電保護素子を開発したと発表した。トランジスター構造を最適化したことで、従来の素子に比べて静電気放電耐量は4倍に向上し、放電耐量のばらつきは12分の1に抑えた。3次元シミュレーションを用いた解析で、耐量が向上したメカニズムも明らかにした。

半導体素子は、帯電した人体などからの静電気放電によって、素子が破壊する可能性がある。このような半導体チップには、静電気破壊を防止するための保護素子が配置されている。ところが、電源電圧や電流が大きくなると保護素子自体もサイズが大きくなり、半導体チップを小型化するのが難しくなっていた。

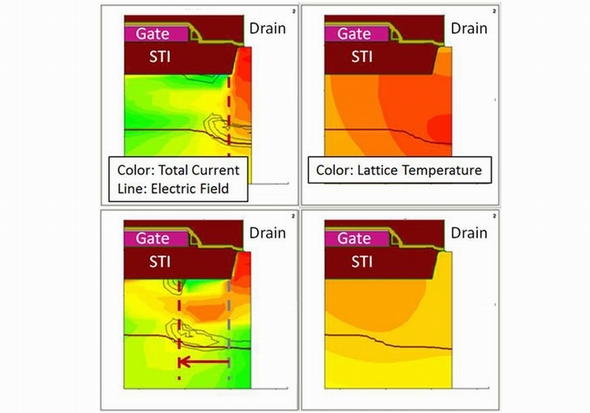

東芝は今回、シリコン内部において電界が集中する箇所を電流が流れ、格子温度が上昇することが熱破壊の主な要因になることを、3次元シミュレーション技術によって解明した。そこで、トランジスターのドレイン側拡散層をソース側に延ばす構造とした。これによって、シリコン内の低抵抗領域を横方向に拡大した。また、高電界箇所のドレイン下部を流れる電流の経路を横方向に広げた。

このような構造とすることで、高電界箇所と電流経路が離れることとなり、静電気放電耐量を従来の4倍に向上させた。放電耐量のばらつきも12分の1に低減することに成功したという。この結果、充電電圧が±2kVの人体モデルに対応する静電気放電保護素子を、従来サイズから32%に縮小することができたという。

東芝は、0.13μm世代のアナログパワー半導体プロセスとして、車載向けを中心とした「BiCD-0.13」(DMOS耐圧は最大100V)、モーター制御向けを中心とした「CD-0.13BL」(DMOS耐圧は最大60V)、電源向けを中心とした「CD-0.13」(DMOS耐圧は最大40V)を、それぞれ用意している。今回開発した技術は、CD-0.13プロセスに適用して2017年度より製品化する予定である。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- TSMCがGaNファウンドリー事業から撤退へ、NavitasはPSMCと提携で対応

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

- 25年5月の世界半導体市場は全地域で成長、19.8%増の590億ドルに

- 危うい再建計画 Wolfspeed、CHIPS法補助金で再生図るか

- 半導体製造ラインの立ち上げ迅速に、日本IBMが京都に開発拠点

- Qualcommの狙いは何なのか、やたらと「高い」Alphawave買収額

- 「DRAM生産の4割を米国で」 Micronを待ち受ける過酷な競争

- 22nmプロセス採用でMRAM内蔵、ルネサスがエッジAI特化の新マイコン

放電保護素子の断面図 出典:東芝

放電保護素子の断面図 出典:東芝 3次元シミュレーションの結果。上段は既存の素子、下段は改良した素子 出典:東芝

3次元シミュレーションの結果。上段は既存の素子、下段は改良した素子 出典:東芝 東芝、3D NAND新工場建設を決定

東芝、3D NAND新工場建設を決定 STT-MRAMでSRAM比1/10以下の消費電力を達成

STT-MRAMでSRAM比1/10以下の消費電力を達成 ワイヤレス充電式の中型電気バス実証走行へ

ワイヤレス充電式の中型電気バス実証走行へ 東芝 低消費のBLE向け無線受信アーキテクチャ

東芝 低消費のBLE向け無線受信アーキテクチャ