ムーアの法則、実質的には28nmが最後か:設計に最も使われているのは65nm以前(1/2 ページ)

7nm、5nmプロセスの実現に向けて微細化の研究開発が進められているが、設計の現場は当然ながら、より現実的だ。28nm以前のプロセスを適用した製品が大半を占め、さらに設計で最も多く使われているのは65nm以前のプロセス、という統計データがある。

“2つの道”に分岐しているプロセス技術

半導体業界では現在、7nmプロセスの微細化実現を目指す製品がごくわずかであるのに対し、28nmプロセス以前の技術を維持している製品が大半を占めている。2年以上前からの予測通り、2つの道に分かれた状況にあるのだ。

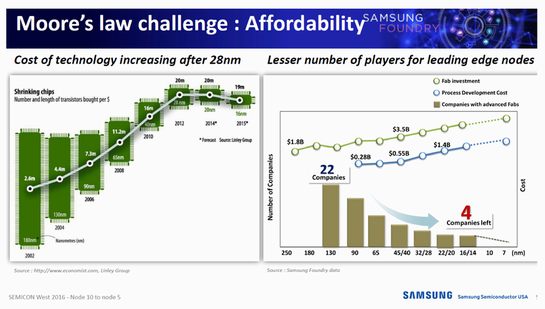

このことから、われわれが2014年3月に投稿したブログ記事「28nm — The Last Node of Moore's Law(ムーアの法則は28nmプロセスで終わる)」の内容が、確証を得たといえるだろう。当時から既に、「28nmプロセス以降も、引き続きトランジスタの微細化は可能だが、コストを抑えることは不可能だ」と主張していたのだ。これについてはSamsung Electronicsが、半導体製造装置と半導体製造用材料に関する北米最大の展示会「SEMICON West 2016」(米国カリフォルニア州サンフランシスコ、2016年7月12~14日)で行ったプレゼンの中で、下図を用いて説明している。

Intelは、「将来的に、プロセス間の移行時間は延びていくが、トランジスタコストは引き続き削減していくことが可能だ」と主張している。しかし、同社はファウンドリーとして成功を収めるには至っていないことから、その主張が正しいとは言い難い。これについて、筆者は以前に、「Intel — The Litmus Test(Intelのリトマス試験)」と題するブログ記事の中で議論を展開している。

また、SemiWiki.comに2016年8月27日付で掲載された記事「Apple will NEVER use Intel Custom Foundry!(AppleはIntelの自社ファウンドリを絶対に利用しない)」も、基本的に同じ内容を提示しているといえる。同記事には、以下のように書かれている。

「Intelは、自社の10nm/7nmプロセス技術の方が、TSMCやSamsungなどの他のファウンドリーよりも優れていると主張するだろう。しかしそれについては、PPAC(電力、性能、シリコン面積、コスト)をベースとしたチップレベルで実証する必要がある。ファウンドリー各社はこれまで、全てのプロセス技術において、SoC(Syste on Chip) PPACベースでIntelを打ち負かしてきた。こうした状況が、10nm/7nmプロセスにおいて変化するとは思えない」

このような議論は今や学術的議論であり、業界に即した議論ではないだろう。実際のところ、半導体業界の大半のメーカーにとって、最先端プロセス技術を適用したデバイスの製造コストは、高額すぎる。この結果、業界では以前からの予測通り、ごく一部の製品だけが7nmプロセスへの微細化を目指し、大半は28nm以前のプロセス技術を採用するという、2つの道に分岐しているのだ。

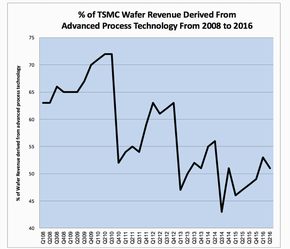

下図は、Ed Sperling氏が2016年8月24日に発表したブログ記事「Stepping Back From Scaling(微細化からの後退)」の中で、TSMCの四半期業績レポートからの引用として掲載されたものである。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- TSMCがGaNファウンドリー事業から撤退へ、NavitasはPSMCと提携で対応

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

- 危うい再建計画 Wolfspeed、CHIPS法補助金で再生図るか

- 25年5月の世界半導体市場は全地域で成長、19.8%増の590億ドルに

- 半導体製造ラインの立ち上げ迅速に、日本IBMが京都に開発拠点

- 「DRAM生産の4割を米国で」 Micronを待ち受ける過酷な競争

- Qualcommの狙いは何なのか、やたらと「高い」Alphawave買収額

- もみ殻と鉱山副産物で「燃料電池用触媒」、白金の代替に