IBM、7nmプロセス向けの新しい絶縁材料を開発:「IRPS」で発表

IBMが7nmプロセス以降の技術に適用できる、新しい絶縁材料を開発したと発表した。SiBCNとSiOCNで構成され、動作電圧を向上させるとする。

7nmプロセス以降の技術に向けて

IBMは、米国カリフォルニア州モントレーで2017年4月2~6日に開催された「IEEE International Reliability Physics Symposium(IRPS)」において、7nmプロセス以降の技術に適用可能な新しい絶縁材料を開発したと発表した。SiBCN(シリコン・ボロン・窒化炭素)とSiOCN(シリコン・酸素・窒化炭素)の2つの材料を使用することで、性能と歩留まりの向上を実現することが可能だという。

また同社は、チップ上のワイヤ間をSiBCNとSiOCNで埋めて、さまざまなライン幅変動(LER:Line Edge Roughness)をモデリングする方法について明らかにした。

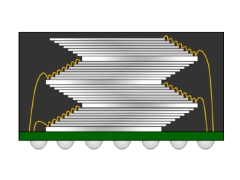

IBM Researchで電気特性化・信頼性部門のマネジャーを務めるJames Stathis氏は、「Time Dependent Dielectric Breakdown of SiN, SiBCN and SiOCN Spacer Dielectric(SiN・SiBCN・SiOCNスペーサー誘電体の時間依存性の誘電破壊)」と題する論文の中で、SiBCNとSiOCNが厚さ10nm(22nmチップ上)および厚さ6nm(7nmテストチップ上)のスペーサー誘電体として、SiNの性能を上回ったことを説明している。同社は、14nmプロセスにおいてSiBCNを、7nmプロセスにおいてSiOCNを、それぞれ採用する予定だという。Stathis氏は、「IBMは、5nmプロセスで究極のインシュレーターとエアギャップを実現したい考えだ」としている。

Stathis氏は、「一般的なSiNスペーサーを使用した場合、最先端プロセス技術の寄生容量は、デバイス容量の約85%となるため、これらの材料の寿命がどのようにチップの動作電圧に依存しているかを、正確にモデリングすることが非常に重要だ。低誘電率の新材料(SiBCNおよびSiOCN)を使用することで、寄生容量を低減できるため、回路性能を向上できる」と述べている。

IBMはこの他にも、「A Stochastic Model for the Impact of LER(LERの影響に関する確率論的モデル)」と「A New and Holistic Modeling Approach for the Impact of Line-Edge Roughness(LERの影響に関する新しい全体的なモデル化法)」という、2つの論文を発表している。これによると、LERも寄生容量の要因の1つになるという。

IBMは論文の中で、ワイヤ間の絶縁体のスペーシングにおいて、LERがどのように不規則に変わり、誘電圧と時間依存性に悪影響を及ぼすかを実証している。IBMは、全体的な確率論的モデルを採用することにより、最先端プロセス適用チップの全体的な信頼性に対する電圧効果を、より正確に予測することが可能になったとしている。

IBMのFabless Reliability Groupのエンジニアたちは、コグニティブコンピューティングアルゴリズムを使用して、これらの新しい絶縁体の誘電破壊点をより正確に予測する方法についても実証している。この新しい手法により、ファウンドリーで製造したチップの実試験における効率を劇的に改善することが可能だという。この技術を適用すれば、新しいファウンドリプロセスの認証前に、スクリーニングとテストシーケンシングを最適化することが可能だ。

【翻訳:田中留美、編集:EE Times Japan】

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -スポンサーからのお知らせ

- PR -Special Contents 2

- PR -記事ランキング

- 25年2Qの半導体企業ランキング、日本勢トップは13位のソニー

- チップ分解で20年をたどる 「万華鏡」のように変化し続ける半導体業界

- 「ファウンドリー事業完全放棄の可能性」、Intel CEOが言及

- 米国半導体の強化は100%関税よりIntel支援 ── 分社発表から1年、結論を急げ

- GaNパワー半導体市場で拡大狙うサンケン電気、パウデックを吸収合併

- 車載半導体ランキング、首位はInfineonでルネサスは5位

- 「現場ですぐ使えるロボット」普及へ、ソニーが自社コア技術を外部提供

- HBMの代替どころか、勇み足で終わりかねない「HBF」

- トランプ関税は「深刻な自滅行為」、最も得をするのは中国

- 容量5TBで帯域65GB/秒、キオクシアのフラッシュメモリモジュール

IBMの「POWER 9」プロセッサの写真。SiBCNやSiOCNの誘電率は、このPOWER 9に使われているSiNよりも低いという 出典:IBM Research

IBMの「POWER 9」プロセッサの写真。SiBCNやSiOCNの誘電率は、このPOWER 9に使われているSiNよりも低いという 出典:IBM Research 進む7nmプロセスの開発、TSMCとIBMが成果を発表

進む7nmプロセスの開発、TSMCとIBMが成果を発表 IBMが7nm試作チップを発表、Intelに迫る勢い

IBMが7nm試作チップを発表、Intelに迫る勢い 人間の脳が握る、デバイス低消費電力化の鍵

人間の脳が握る、デバイス低消費電力化の鍵 Intel、モバイル向けSoC事業を廃止

Intel、モバイル向けSoC事業を廃止 半導体業界がポストCMOS開発に本腰

半導体業界がポストCMOS開発に本腰