TSMCの高性能・高密度パッケージング技術「CoWoS」(前編):福田昭のデバイス通信(106) TSMCが解説する最先端パッケージング技術(5)(1/2 ページ)

今回から前後編に分けて「CoWoS(Chip on Wafer on Substrate)」を解説する。CoWoSの最大の特長はシリコンインターポーザを導入したことだが、では、なぜシリコンインターポーザが優れているのだろうか。シリコンインターポーザに至るまでの課題と併せて説明する。

この記事は会員限定です。会員登録すると全てご覧いただけます。

シリコンインターポーザを必要としたHPC向けパッケージ

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンダリ最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

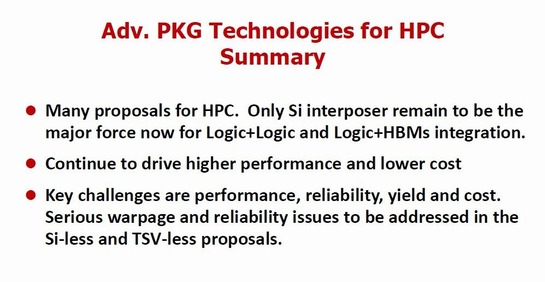

前回は、2012年から2016年までの高性能コンピューティング(HPC:High Performance Computing)向け高密度パッケージング技術の進展を要約して説明した。2012年にTSMCが開発したパッケージング技術「CoWoS(Chip on Wafer on Substrate)」は、2016年に至るまでずっと、主流であり続けた。ロジックダイとロジックダイを高密度に並べたり、ロジックダイとDRAMモジュール「HBM(High Bandwidth Memory)」を高密度に並べたりする最先端パッケージは、CoWoS技術のキーパーツであるシリコンインターポーザを必要とし続けた。

プリント基板実装では高周波・高速信号の伝送が難しい

HPC向けの高密度パッケージング技術「CoWoS」が主流であり続けたのは、この技術が優れていたことの証明でもある。そこであらためて、CoWoS技術の概要を説明したい。

CoWoS技術の本質は、シリコンダイを近接して並べることで、プリント基板における占有面積を減らすこと、言い換えると半導体チップの実装密度を高めることにある。従来は、半導体デバイスはシリコンダイを樹脂封止した状態で、プリント基板に個別に実装するのが普通だった。隣接する半導体チップ(シリコンダイ)の間隔は短くても、20mmくらいの長さがあった。実配線長はさらに長くなる。50mm前後の長さは珍しくない。

20mm(2cm)~50mm(5cm)くらいの長さは、プリント基板の配線を伝わる信号の周波数が低いとき(およびデータ転送速度が低いとき)にはまったく問題にならなかった。しかし信号の周波数が1GHz(あるいは1Gビット/秒)を超えるようになると、配線の寄生素子(配線の抵抗や容量、インダクタンス)が信号の波形をひずませることや、配線に電流を流すためのドライバ素子(出力バッファ)による消費電力の増加などが無視できなくなった。

高周波・高速の信号を高品質に伝送しながら、消費電力を抑えるためには、配線長を短くしたい。この最も単純で効果的な手段は、隣接するシリコンダイの距離を縮めることである。そのためにはまず、樹脂封止をせずにシリコンダイのままでプリント基板に実装したい。さらに、シリコンダイ間の距離は数mm以下に縮めたい。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「AppleがSamsungから半導体調達」報道、ソニーの反応は

- 「GaNのコストは5年以内にSi並みに」 ロームの勝ち筋は

- タイワン・セミコンダクターがSiCパワー半導体市場に参入、その狙いは

- 2024年のイメージセンサー市場もソニーがトップ、高まる中国の存在感

- 世界半導体市場は2025年6月も成長継続 日本は減少

- Teslaとの契約はSamsungを回復に導くのか

- 世界半導体製造装置市場、2026年は過去最高に

- RC-IGBTとSiC、ダイでもモジュールでも 東芝の車載パワー半導体

- ウエハーの傷にだけ色付けして撮影、検査スピードは数百倍に 東芝

- アオイ電子がシャープ三重第2工場も買収、先端半導体パッケージ強化