TSMCの高性能・高密度パッケージング技術「CoWoS」(後編):福田昭のデバイス通信(107) TSMCが解説する最先端パッケージング技術(6)(1/2 ページ)

「CoWoS(Chip on Wafer on Substrate)」の解説の後編では、パッケージの構造とパッケージの製造工程について説明する。パッケージの信頼性を大きく左右するのが、シリコンインターポーザの反りだが、CoWoSの製造工程では、この反りを抑えることができる。

数GHzあるいは数Gbit/秒の高周波・高速伝送に対応

2016年12月に開催された国際学会IEDMのショートコース講演(技術解説講演)から、「システム集積化に向けた最先端パッケージング技術(Advanced Packaging Technologies for System Integration)」と題する講演の概要をシリーズでご紹介している。講演者はシリコンファウンダリ最大手のTSMCでシニアディレクターを務めるDouglas Yu氏である。なお講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Yu氏の講演内容を筆者が適宜、補足している。あらかじめご了承されたい。

前回は、TSMCが開発した高性能・高密度パッケージング技術「CoWoS(Chip on Wafer on Substrate)」の目的と、その効果を説明した。すなわち、「CoWoS技術ではシリコンインターポーザの導入により、隣接するシリコンダイの距離をわずか0.03mm(30μm)にまで詰められる。数GHzあるいは数Gビット/秒と高周波・高速の信号伝送を可能とする」(前回の内容から引用)のである。さらに付け加えれば、シリコンダイが搭載する出力バッファは、隣接するシリコンダイが出力先であると分かっている場合は、電流駆動能力をあまり増やさずに済む。これは消費電力の低減につながる。

今回は、CoWoS技術によるパッケージの構造と、パッケージの製造工程を説明する。

3階層の接続構造を採るCoWoS技術のパッケージング

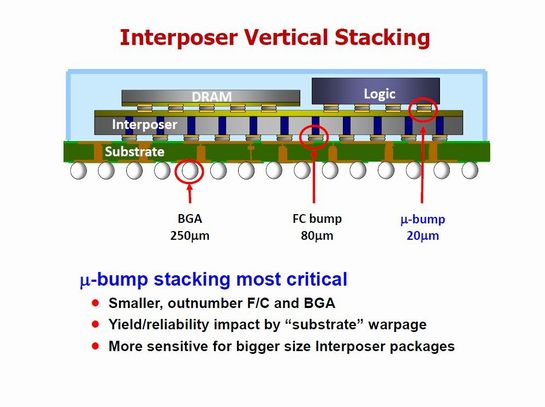

CoWoS技術によって複数のシリコンダイを高密度に実装したパッケージは、主に3つの階層に分かれている。プリント基板側から説明すると、2次元マトリクス(エリアアレイ)状に配置した数多くのハンダボール(BGA:Ball Grid Array)がパッケージの樹脂基板とプリント基板をつないでいる。ハンダボールの直径は約250μm。これが最初の階層である。

パッケージの樹脂基板の上には、シリコンインターポーザが載っている。パッケージ基板とシリコンインターポーザの間は、フリップチップ接続に使われるバンプによってつなぐ。バンプの直径は約80μm。これが2番目の階層である。パッケージの樹脂基板は、スルーホールを備えた両面基板あるいは4層基板であることが多い。シリコンインターポーザの下部電極は、シリコン貫通電極(TSV)によって上部電極と電気的に接続する。

シリコンインターポーザの上部は4層程度の高密度な配線層になっており、最上層の電極とマイクロバンプを介してシリコンダイの入出力パッドと接続する。マイクロバンプの直径は約20μm。これが3番目の階層である。シリコンダイの入出力パッドの配置は、エリアアレイあるいは、四隅に寄せたアレイである。実際にはエリアアレイであることが多い。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -記事ランキング

- 中国はどうEVバッテリー市場を支配したか 欧米のミスは「固体電池への幻想」

- 「充電5分で520km走行」を巡る疑問、 中国CATLの車載バッテリー発表を考察

- ロームのSiC搭載インバーター部品が量産開始、中国大手の新型EVに

- NEDOの手を離れ本格ビジネスへ レゾナックが27社参画の「JOINT3」設立

- 「メモリの壁」突破でエッジAIを次の段階に、CEA-LetiとST幹部が語る

- 米国の中国向け装置輸出「特例撤回」 SamsungとSKへの影響は

- GaNで半導体製造の欠陥検出 キオクシア岩手で検証へ

- あと5年で中国が半導体生産能力トップに 米国は先端ノード強化

- DRAM市場首位のSK hynix、量産用高NA EUV初導入で競争力強化

- 「中国の小さなNVIDIA」、Cambriconの躍進が示す中国の野心