EE Times Japan >

メモリ/ストレージ >

究極の高密度不揮発性メモリを狙う強誘電体トランジ...

究極の高密度不揮発性メモリを狙う強誘電体トランジスタ:福田昭のストレージ通信(73) 強誘電体メモリの再発見(17)(1/2 ページ)

今回は、1個のトランジスタだけでメモリセルを構成できる「FeFET(Ferroelectric FET)」または「強誘電体トランジスタ」について解説する。FeFETは、構造はシンプルだが、トランジスタの設計はかなり複雑になる。

» 2017年09月05日 10時30分 公開

[福田昭,EE Times Japan]

強誘電体を電界効果トランジスタのゲート絶縁膜に導入する

本シリーズの第17回(前々回)では、強誘電体を使ったメモリセルの構造について簡単に説明した。1つはDRAMと似た構造のセルで、1個のトランジスタと1個の強誘電体キャパシターで構成する。トランジスタがセル選択素子、強誘電体キャパシターが記憶素子、という役割り分担になる。

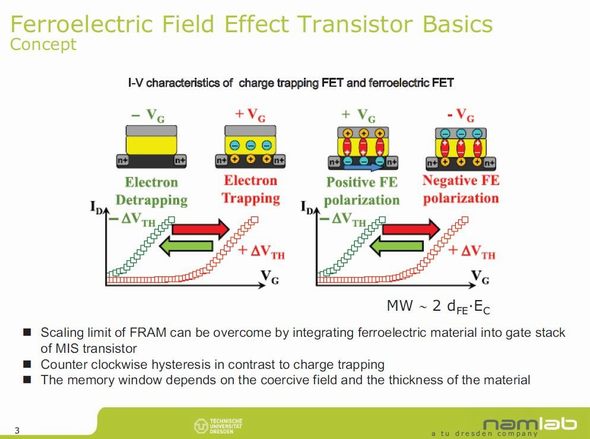

もう1つは電荷捕獲(チャージトラップ)方式フラッシュメモリと似た構造のセルで、MOSトランジスタ(MOSFET)のゲート絶縁膜を強誘電体にすることで、1個のトランジスタだけでメモリセルを構成する。強誘電体ゲート絶縁膜のトランジスタ(FET)が、セル選択素子と記憶素子の両方を兼ねる。このようなトランジスタを「FeFET(Ferroelectric FET)」「強誘電体トランジスタ」などと呼んでいる。1個のトランジスタだけでメモリセルを構成できるので、究極ともいえる、高密度なメモリを原理的には実現可能だ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- Xiaomi 15S Proを分解、10年かけて磨き続けた半導体開発力

- 半導体のネガティブイメージ解消へ、ソニーやキオクシアら国内大手が集結

- 「充電5分で520km走行」を巡る疑問、 中国CATLの車載バッテリー発表を考察

- 中国半導体装置展示会「CSEAC」レポート 中工程シフトと“露光回避”の実態

- 創刊前の20年間(1985年~2005年)で最も驚いたこと:「高輝度青色発光ダイオード」(前編)

- 「鉄とマンガン」が半導体の微細化を進化させる?

- 「CEATEC 2025」ことしも10万人超えへ 吉村知事が万博語るセッションも

- TO-247より省面積、ロームの新SiCパワーモジュール

- STがパネルレベルパッケージの試作ライン新設へ 6000万ドル投じ

- SiFiveの新RISC-VコアはAI特化 メモリ管理の革新で性能向上