EE Times Japan >

メモリ/ストレージ >

二酸化ハフニウムを使った強誘電体トランジスタの研...

二酸化ハフニウムを使った強誘電体トランジスタの研究開発(後編):福田昭のストレージ通信(77) 強誘電体メモリの再発見(21)(1/2 ページ)

後編では、二酸化ハフニウム系強誘電体トランジスタ(FeFET)の特性について見ていこう。動作電圧やデータ書き込み時間などは十分に良い特性だが、長期信頼性については大幅な改善が必要になっている。

» 2017年09月21日 09時30分 公開

[福田昭,EE Times Japan]

従来型材料と二酸化ハフニウムのFeFETの大きな違い

前回は、新材料である「二酸化ハフニウム系強誘電体材料」を使った強誘電体トランジスタ(FeFET)の始まりと特徴を概観した。

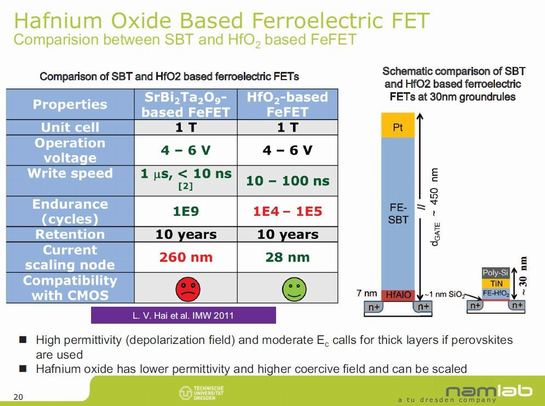

従来型材料によるFeFETの特性と二酸化ハフニウム系材料によるFeFETの特性を比較すると、両者の違いが浮き彫りになってくる。なお、以降に登場する数値は全て、研究室レベルの値である。

SBT(タンタル酸ビスマス酸ストロンチウム)ベースのFeFET(表中の左列)と二酸化ハフニウムベースのFeFET(表中の右列)の主な特性。右の図は、最小加工寸法を30nmと仮定した場合に両方のFeFETのゲート構造とゲート高さを描いた図。二酸化ハフニウムベースのFeFETはゲートが極めて薄いことが分かる。出典:NaMLabおよびドレスデン工科大学(クリックで拡大)

SBT(タンタル酸ビスマス酸ストロンチウム)ベースのFeFET(表中の左列)と二酸化ハフニウムベースのFeFET(表中の右列)の主な特性。右の図は、最小加工寸法を30nmと仮定した場合に両方のFeFETのゲート構造とゲート高さを描いた図。二酸化ハフニウムベースのFeFETはゲートが極めて薄いことが分かる。出典:NaMLabおよびドレスデン工科大学(クリックで拡大)従来型材料(SBT:タンタル酸ビスマス酸ストロンチウム)によるFeFETの特性そのものは、かなり良好である。動作電圧は、4V~6Vとそれほど高くない。データの書き込みに必要な時間は1マイクロ秒であり、10ナノ秒というデータもある。そして書き換え可能回数は108サイクルに達する。データ保持期間は、10年を確保できる。

ただし、大きな問題点が1つある。最小加工寸法が260nmにとどまることだ。28nm/20nmといった最小加工寸法がCMOSロジックでは標準的に使われている現在、260nmというゲート長は大き過ぎる。CMOSロジックとの混載は商業的に困難であり、単体のメモリとしても記憶容量当たりのシリコン面積が大き過ぎて製造コストが極めて高くついてしまう。

その点、二酸化ハフニウム系材料のFeFETは、既に28nmの最小加工寸法で試作されている。CMOSロジックとの混載は比較的容易であり、単体メモリとしての密度もかなり期待できる。原理的には20nm技術や16nm技術での製造も可能だ。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 2

- PR -記事ランキング

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- 自律神経から「頑張りすぎ」を可視化、村田製作所

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- 暗い夜道でも120m先の歩行者を検知、キヤノンが新SPADセンサー

- 商用化から40年を迎えたFPGA、次の主戦場はエッジAI

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- JDIの液晶の知見、先端半導体パッケージングの中核技術に

- 「NVIDIAと真逆の取り組みをしよう」 Jim Keller氏

- 自動運転のキーデバイスとなる車載SoC