「RISC-V」はEmbeddedでマーケットシェアを握れるのか:RISC-V Day 2017 Tokyo(3/5 ページ)

RISC-Vと親和性が高いアーキテクチャを開発する台湾ベンダー

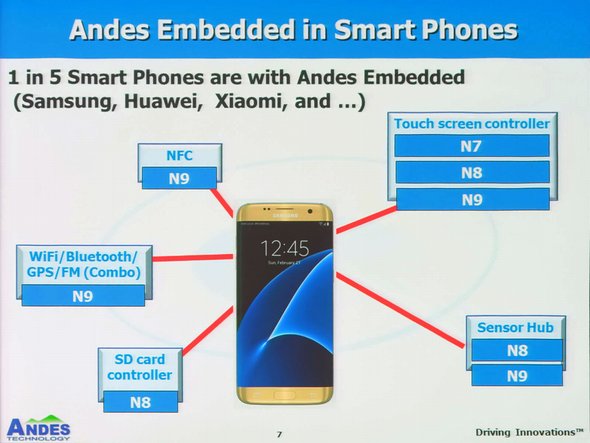

2つ目はAndes TechnologyのCharlie Hong-Men Su博士(写真13)のセッションから。Andes Technologyは台湾ベースのCPU IPのベンダーで、意外に(というと失礼だが)多くのクライアントを持つ。創業は2005年と比較的若い会社であるが、「AndeStar V1」~「同V3」という独自のアーキテクチャと、これを実装した「N7」~「D15」までのさまざまなIPを提供している。特にN7~N9のMCU IPは多くの機器で採用されているとする(写真14)。

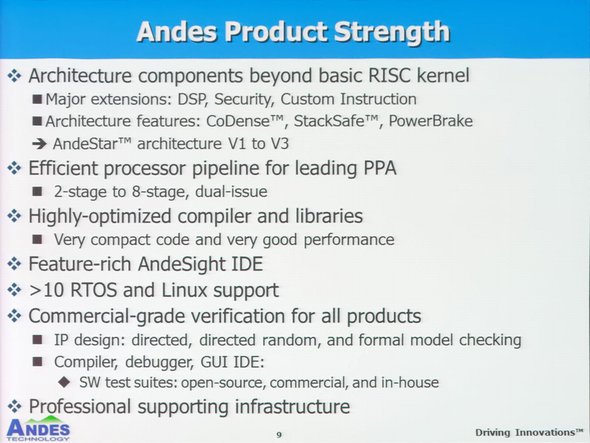

これまでは独自のISAとこれをサポートするアーキテクチャやIP、そしてソフトウェア環境を提供してきた訳だが(写真15)、2017年5月にまずRV64IをサポートしたAndeStar V5アーキテクチャと、これを実装したAndesCore NX25を発表する(参考リリース)。

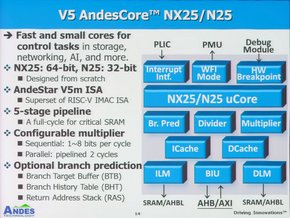

TSMCの28nmプロセスで67KGateという規模、そして1GHz以上の動作周波数と17μW/MHzという比較的低めの消費電力がアピールされており、この当時は「32bitは既存のままで、64bitのみRISC-Vに乗り換えた」と筆者は理解していた。ただ実際には同時にRV32Iに基づくAndeStar V5mも開発されていたようで、こちらを実装したAndesCore N25もラインアップに加わり、2017年11月にはImperas/Lauterbach/Mentor/UltraSoCといったベンダーによるサポートも加わっている(参考)。

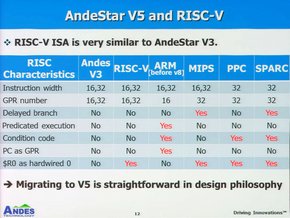

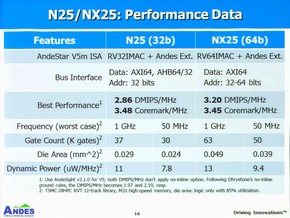

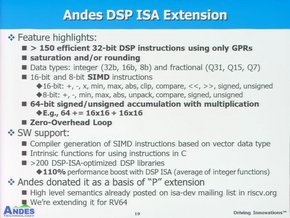

さて、Su博士によればRISC-V(RV32I/RV64I)は、AndeStar V3と非常に親和性が高かったとする(写真16)。ただ、だからといってAndeStar V3ベースのコアのデコーダー部だけを入れ替えたのではなく、やはりフルスクラッチで開発したとの事(写真17)。性能は写真18の通りで、50MHz程度を狙うのであればゲート数も30K、TSMCの28nmで0.024mm2だから、そう悪い数字ではない。ちなみにAndesではDSP拡張を自身で行っており、これを利用することで110%の性能改善が実現したとしている(写真19)。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- 「Switch 2」を分解 NVIDIAのプロセッサは温存されていた?

- ルネサスがWolfspeedの再建支援、Q2には2500億円の減損か

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?

- 「N2」SRAMの歩留まりは90%以上 技術開発も好調のTSMC

- コンチネンタルが半導体を自社開発へ、製造はGF

- TELとimecが「戦略的パートナーシップ」を5年延長

- 「Rapidusを支援したい」 VCに転身のPat Gelsinger氏、日米の協業に意欲

- 全固体電池の容量劣化メカニズム マクセルが解明

- 2nm半導体設計基盤でRapidusとシーメンスが協業

- 京大やトヨタなど、全固体フッ化物イオン二次電池用正極材料を開発

写真13:Andes TechnologyのCTO兼SVP、RD&TMのCharlie Hong-Men Su博士

写真13:Andes TechnologyのCTO兼SVP、RD&TMのCharlie Hong-Men Su博士