「RISC-V」はEmbeddedでマーケットシェアを握れるのか:RISC-V Day 2017 Tokyo(4/5 ページ)

RISC-Vを商用化するSiFive

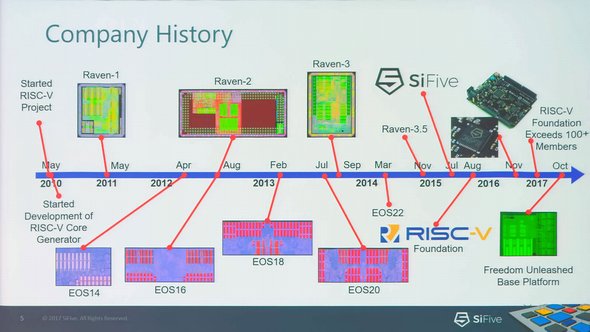

3つ目はSiFiveのJack Kang氏によるセッションである。SiFiveは、いわばRISC-Vを商用化するための会社であり、「E31」「E51」「U54-MC」という3種類のIPを提供する他、「Freedom SoC」と呼ばれるこのIPを実装したSoC、さらには、このFreedom SoCを搭載した「HiFive 1」という開発ボードの提供も開始している(写真21)。

写真21:もともとのRaven ProjectからそのままRISC-Vの開発にシフトしたメンバーがそのままSiFiveに在籍して開発を行っていることもあって、Company HistoryがRaven-1から始まっているのは、さすがである(クリックで拡大)

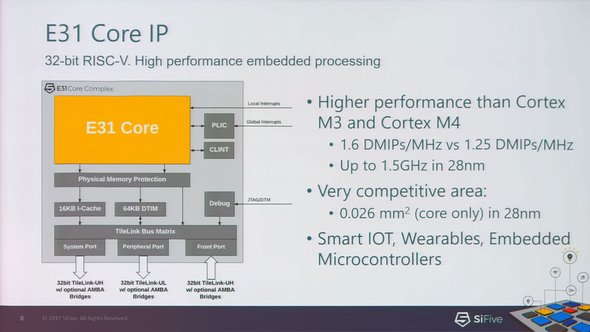

写真21:もともとのRaven ProjectからそのままRISC-Vの開発にシフトしたメンバーがそのままSiFiveに在籍して開発を行っていることもあって、Company HistoryがRaven-1から始まっているのは、さすがである(クリックで拡大)さてそのSiFive、EシリーズがEmbedded MCU向け、Uシリーズがアプリケーションプロセッサ向けという扱いで、なのでEシリーズは仮想記憶のサポートもなくMPU(Memory Protection Unit)のみ、一方のUシリーズは仮想記憶やMMUのサポートありといった違いがある。最小構成のE31 Core(写真22)は、それでもターゲットはCortex-M3/M4クラスを狙っているのが分かる。

写真22:足回りは独自のTileLinkである。TileLinkの説明は、「FPGA開発日記」著者の@msyksphinz氏(氏も「RISC-Vオープンソースハードウェア概説」という講演を行っており、これもまた大変に面白かった)の2017年7月13日の記事が分かりやすいと思う(クリックで拡大)

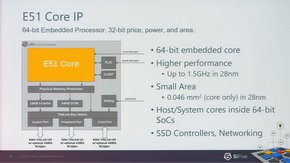

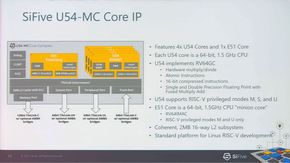

写真22:足回りは独自のTileLinkである。TileLinkの説明は、「FPGA開発日記」著者の@msyksphinz氏(氏も「RISC-Vオープンソースハードウェア概説」という講演を行っており、これもまた大変に面白かった)の2017年7月13日の記事が分かりやすいと思う(クリックで拡大)E51 Coreはさらに高性能な、しかも64bitのコアである(写真23)。これに対してU54-MCは、Quad U54+E51というマルチコア構成のIPである(写真24)。こちらは本当にアプリケーション向けプロセッサで、性能的に言えば例えば(MACOMの買収後に別ファンドに売っ払われて、ついに最近サイトのアクセスまでできなくなってしまった)旧Applied MicroのX-Geneとかに近い感じである。

左=写真23:性能ターゲットはCortex-M7クラスに相当するように思われる。あるいはCortex-A5クラスか。SSD ControllerとかNetworkingといえばそのあたりだろう/右=写真24:別にbig.LITTLE的な動作ではなく、U54がアプリケーション処理、E51がI/O管理といった使い方を想定していると思われる(クリックで拡大)

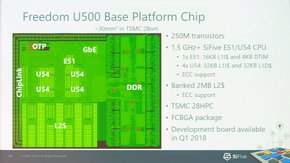

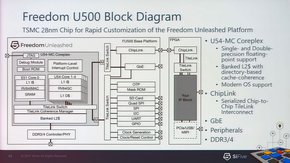

左=写真23:性能ターゲットはCortex-M7クラスに相当するように思われる。あるいはCortex-A5クラスか。SSD ControllerとかNetworkingといえばそのあたりだろう/右=写真24:別にbig.LITTLE的な動作ではなく、U54がアプリケーション処理、E51がI/O管理といった使い方を想定していると思われる(クリックで拡大)このU54-MCにメモリコントローラーや周辺I/Oを組み込んだFreedom U500のダイサイズが30mm2というのは、かなりコスト競争力のありそうな構成である。Armで言えば、Cortex-A53×1~2coreのSoCと競合という感じになるのではないかと思われる(写真25)。内部構造はこんな感じ(写真26)で、ChipLink経由でFPGAなどを使ってまず自分のIPを実装して検証を行い、うまくいく様ならIPをSiFiveから購入、自分のIPも組み込んでSoCを開発する、といったシナリオを考えているようである。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -- EE Times Japanテ勇DN Japan 邨ア蜷磯崕蟄千沿�� 蜊雁ー惹ス捺・ュ逡� 縺薙l縺セ縺ァ縺ョ20蟷エ縲√%繧後°繧峨�20蟷エ窶補� 髮サ蟄千沿2025蟷エ6譛亥捷

- 繧「繝励Μ繧ア繝シ繧キ繝ァ繝ウ縺ョ隕∽サカ縺ォ蠢懊§縲√す繧ー繝翫Ν繝√ぉ繝シ繝ウ縺ョ豸郁イサ髮サ蜉帙r蜑頑ク帙☆繧区婿豕�

- 菴取カ郁イサ髮サ蜉幢シ城ォ倡イセ蠎ヲ縺ョ繧キ繧ー繝翫Ν繝√ぉ繝シ繝ウ縲∵ウィ諢上r謇輔≧縺ケ縺阪ち繧、繝溘Φ繧ー隕∝屏縺ィ縺ッ��

- Intel縲∽サ翫←縺�↑縺」縺ヲ繧具シ溘闍ヲ蠅�r謚懊¢蜃コ縺帙k縺�

- 繝代Ρ繝シ蜊雁ー惹ス薙〒豕ィ逶ョ縺ョGaN縲√ヱ繝ッ繝シ繧「繝ウ繝励ユ繧ケ繝医�隱イ鬘後→譛驕ゥ縺ェ繧「繝励Ο繝シ繝�

Special Contents 1

- PR -記事ランキング

- 「Switch 2」を分解 NVIDIAのプロセッサは温存されていた?

- ルネサスがWolfspeedの再建支援、Q2には2500億円の減損か

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?

- 「N2」SRAMの歩留まりは90%以上 技術開発も好調のTSMC

- コンチネンタルが半導体を自社開発へ、製造はGF

- TELとimecが「戦略的パートナーシップ」を5年延長

- 「Rapidusを支援したい」 VCに転身のPat Gelsinger氏、日米の協業に意欲

- 全固体電池の容量劣化メカニズム マクセルが解明

- 2nm半導体設計基盤でRapidusとシーメンスが協業

- 京大やトヨタなど、全固体フッ化物イオン二次電池用正極材料を開発

写真20:SiFiveのVP, Product and Business DevelopmentのJack Kang氏

写真20:SiFiveのVP, Product and Business DevelopmentのJack Kang氏