半導体プロセスの微細化は利益につながるのか:米で専門家が議論(1/2 ページ)

今後、半導体プロセスの微細化を進めていく上で、「微細化が本当に利益につながるのか」という疑問が出ているようだ。

微細化で利益を出せるのか

エンジニアたちには今後、5nm/3nm/2nmプロセス技術の実現に取り組んでいく上で、幾つかの選択肢が用意されている。しかし、「利益を絞り出すことができるのかどうかは、5nmプロセスでさえも定かでない」とする声が上がっているようだ。

現在、半導体チップのさらなる小型化を実現するためには、複雑さとコストが増大する一方であることから、減速の傾向が強まりつつある。Qualcommの設計技術チームでエンジニアリング担当シニアディレクターを務めるPaul Penzes氏は、Synopsysユーザーグループのイベント会場において、パネル討論に参加し、「モバイルプロセッサのクロック周波数は3GHzでピークに達し、面積と消費電力の点で得られる利点も、7nmプロセス以降は少なくなっていくとみられている」と述べている。

また同氏は、「10mmプロセスでは16%の高速化を実現できているケースもあるが、7nmプロセスでは、金属配線の抵抗が障壁となるだろう。低消費電力化にしても、10nmプロセスでは30%減となったが、7nmプロセスでは10~25%減と、減少幅が少なくなる見込みだ。小型化については、10nmプロセスの37%減から、7nmプロセスでは20~30%減にとどまるとみられている」と述べる。

エレクトロニクス業界はこれまで数十年間にわたり、いわゆる「ムーアの法則」を実現する形で、集積回路に搭載する素子の数を増やしてきた。その結果、PCからスマートフォンに至るさまざまな製品において、かつてないほどの小型化と高速化、低コスト化が迅速に達成されてきたのである。

Penzes氏は、「面積に関しては、現在も堅調に小型化が進んでいるが、マスクのコストなどが増加していることから、実際のコストの優位性や技術改良の速度は減り始めている。5nmプロセスで、どんな利点が残るのかは現時点では不明だ。5nmプロセスは、単に7nmプロセスの拡張版にすぎないという可能性もある」と指摘する。

FinFETの限界は

SynopsysとSamsung Electronicsの技術者たちは、パネル討論において、「既存のFinFETは、5nmプロセスでも使われるだろう。FinFETは、フィン幅が約3.5nmを下回った時点でハードウェア的限界に達するとみられている」と述べている。

Synopsysのフェローを務め、トランジスタの専門家であるVictor Moroz氏は、「設計者たちは今後、薄い水平ナノワイヤを、恐らく3層、積層する方向に移行していく必要があるだろう。これに関してはSamsungが、4nmプロセス向けにゲートオールアラウンド(GAA)トランジスタを使用し、2020年までには製造を開始する計画であると発表している。

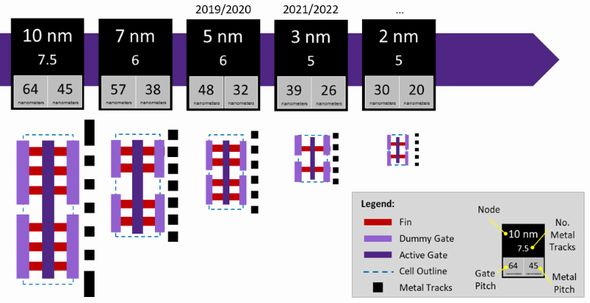

Moroz氏は、「ピッチの微細化は今後、1世代当たり約0.8倍に減速していく見込みだ。このためセルの高さは、7nmプロセスでは2フィン/6トラックで約228nmだが、3nm/2nmプロセスでは5トラック/1フィンで130~100nmまで縮小しなければならない」と述べる。

さらに同氏は、「このような技術を適用すれば、2nmプロセスまで微細化できる可能性は高まる。それ以降は、グラフェンなどを活用していくことになるだろう」と語った。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- 暗い夜道でも120m先の歩行者を検知、キヤノンが新SPADセンサー

- 自律神経から「頑張りすぎ」を可視化、村田製作所

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- 自動運転のキーデバイスとなる車載SoC

- キオクシアが攻める「NANDとDRAMのあいだ」 NVIDIAと協業も

- 次はデータセンター 「スマホ以外」にも手を広げるQualcomm