16nm世代FPGA、ザイリンクスが「UltraScale+」ファミリを発表:プログラマブルロジック FPGA(2/3 ページ)

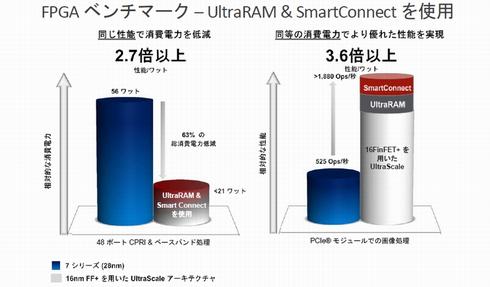

ザイリンクスは、16nmプロセス技術を用いた次世代FPGA「UltraScale+」ファミリを発表した。従来の28nmプロセスFPGA/SoCに比べて、消費電力当たり2〜5倍のシステム性能を実現することが可能となる。

「UltraRAM」、「SmartConnect」技術でシステム性能をさらに向上

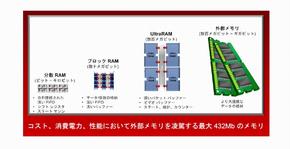

16nm UltraScale+FPGAで新たに採用されたUltraRAMは、最大432Mビットの容量まで実装できるコンフィギュレーション可能なSRAMである。これまでのオンチップメモリは容量が最大数十メガビットに限られていた。それ以上のメモリ容量が必要な場合は、外部メモリで拡張するしかなかった。UltraRAMは大容量のメモリを演算回路の近い場所に実装できるため、システム性能の向上を可能とした。「従来の内蔵RAMと外部RAMの容量差のギャップを埋めることができる」(Erjavec氏)と話す。

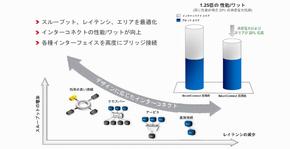

SmartConnectは、FPGA内部における機能ブロック間の接続を、設計ツール側で自動的に最適化する機能だ。「スループット」や「レイテンシ」、「チップ面積」といった、設計要件の優先度に基づいて、インターコネクトトポロジの最適化を行い、直接接続やアービタ、クロスバーなどのインターコネクト技術を使い分ける。これによって、バスのボトルネックを改善/解消し、消費電力当たり1.25倍の性能を得ることができるという。従来と同等の性能でよければ、消費電力およびインターコネクトに必要なチップ面積を20%も節減することが可能となる。

次世代FPGA「UltraScale+」ファミリに搭載されたメモリ技術「UltraRAM」(左)と、インターコネクト技術「SmartConnect」(右)の概要 (クリックで拡大) 出典:ザイリンクス

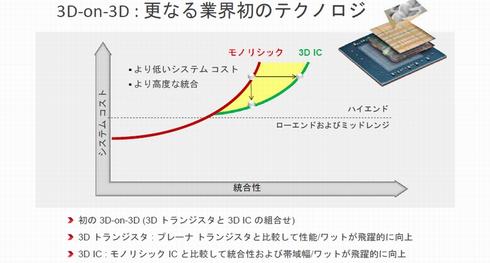

次世代FPGA「UltraScale+」ファミリに搭載されたメモリ技術「UltraRAM」(左)と、インターコネクト技術「SmartConnect」(右)の概要 (クリックで拡大) 出典:ザイリンクスVirtex 16nm UltraScale+FPGAは、UltraRAMやSmartConnectといった新たな技術基盤に加えて、「3D-on-3D」技術を導入した。3D-on-3Dとは、同社で3世代目に当たる3D IC技術と、3次元構造を持つTSMCの16FF+を組み合わせた技術で、ミッドレンジのKintexに比べて性能や集積度、帯域幅などをさらに向上している。

Copyright © ITmedia, Inc. All Rights Reserved.