CMOSが拓く次の応用 〜 ISSCC 2009開催:アナログ設計(5/5 ページ)

第4部 A-D変換器は「脱オペアンプ」へ、低電力維持しつつ高精度・高速化

ISSCC 2009のデータ・コンバータ(A-D変換器/D-A変換器)分野では、前回(ISSCC 2008)のようなエネルギ効率競争は影を潜め、「脱オペアンプ(演算増幅器)」の流れの中で、消費電力を低く維持しつつも高速化、高精度化への着実な進歩が見られ、実用性が高まった。

今回、特に注目したいのは、パイプライン型A-D変換器に再びスポットライトが当たり始めたことである。パイプライン型A-D変換器は従来、高速・高精度のA-D変換方式の主流を担っていたが、近年は性能改善が足踏み状態にあった。半導体プロセス技術の微細化に起因した課題が表面化したからである。すなわち、トランジスタの微細化によって、オペアンプの利得を確保しにくくなり直線性が劣化する、電源電圧の低下によって、信号の電圧振幅が小さくなりSN比が低くなる、それを防ぐためにスイッチト・キャパシタ回路を構成するコンデンサの静電容量を大きくすると消費電流が増大する、といった課題である。

このためここ数年は、オペアンプを使わずに構成できる逐次比較(SAR)型A-D変換器に注目が集まっていた。定常電流を流さずに済み、論理回路と同様の回路で構成可能なこともあり、微細化に適しているとみられたからだ。変換速度や変換精度などの性能当たりの消費電力の低減を目指す「低エネルギ化競争」が加速し、昨年のISSCC 2008ではFOM(Figure of Merit)が1変換ステップ当たり4.4fJと極めて低い、驚異的なSAR型A-D変換器が発表された†1)。

ただし、SAR型A-D変換器は動作原理上、1回のA-D変換に多数のクロック・サイクルを費やす必要があり、高速化には限界がある。このためISSCC 2008では、インターリーブと呼ぶ手法を用いた高速化が脚光を浴びた。低消費エネルギ特性に優れたSAR型A-D変換器コアを数多く用意しておき、各コアを標本化タイミングをずらしながら動作させることで、等価的に変換速度を高める。しかしこの手法には、専有面積の増加を招くことや、回路のオーバーヘッドが大きく、チップ全体で見るとFOMが著しく劣化してしまうという課題があることが明らかになった。

こうした経緯からISSCC 2009では、インターリーブ動作を使わずに高速化が図れるという、パイプライン型の特徴を生かした成果の発表が相次いだ。

オペアンプ・レスの実用性が高まる

まず注目したいのは、米Massachusetts Institute of Technology(MIT)が発表したパイプライン型A-D変換器である(講演番号は9.3)。分解能は12ビット、変換速度は50Mサンプル/秒、消費電力は4.5mWで、精度と速度、消費電力ともに十分な性能を達成しており、実用性は非常に高い。2006年のISSCC 2006で同大学のHae-Seung Lee教授らが提案した「Zero Cross Detector(ZCD)」と呼ぶ回路方式を基に、今回は実用性を高める改良を施した。

一般にパイプライン型では、変換処理に必要な電荷をコンデンサとオペアンプを使って次段に転送するという処理を多段にわたって繰り返す。このオペアンプと同等の役割を果たす回路を、電流源と比較器を使って構成したものがZCDである†2)。オペアンプを使う場合に比べて高い変換速度が期待でき、極めて小さい電力で動作する可能性があるものの、精度などに難点があり、実用にはまだ遠かった。

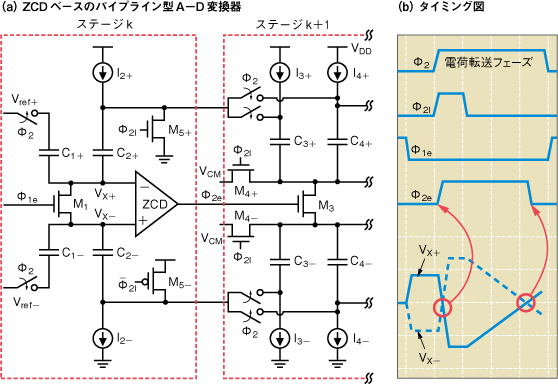

今回MITが発表したパイプライン型A-D変換器の主要部分の回路構成と動作タイミング図を図1に示す。従来はシングルエンド型の回路構成を採っていたが、電源雑音や基板雑音に弱かったため、今回は完全差動型とした。また、基準電圧との比較方式についても、従来提案していたデュアル・スロープ(二重積分)型から、より簡素なシングル・スロープ(積分)型に変更した。パイプライン各段の単位A-D変換回路は、3ビット相当の構成になっているようだ。デジタル出力電圧に対するSN比の評価結果を見ると、前回発表のシングルエンド構成ではデジタル出力電圧が0.8V上昇するとSN比が40dBから37dBへと劣化していたが、今回の差動構成では1.3V上昇させてもSN比は72dB程度のままほとんど変化しておらず、高い雑音耐性が実証された。

図1 差動化で雑音耐性を高めたZCDベースのパイプライン型 (a)は、オペアンプの代わりに「Zero Cross Detector(ZCD)」を使ったパイプライン型A-D変換器の差動構成の回路図である。(b)はこのA-D変換器の動作タイミング図を示す。電荷転送フェーズではまず、プリチャージ信号φ2IがスイッチM3とM4±、M5±をオンに切り替えて、コンデンサC3±とC4±の充電状態を初期化する。次にφ2IがM4±とM5±をオフに切り替えると、電流源I2±とI3±、I4±がC3±とC4±を充電し始める。ZCDの差動入力端子の電位が一致(ゼロ交差)すると、ZCDの出力信号φ2eがM3をオフに切り替えて、コンデンサへの充電を停止し、次のステージで残留電荷のサンプリングを開始する。出典:米Massachusetts Institute of Technologyの発表資料

図1 差動化で雑音耐性を高めたZCDベースのパイプライン型 (a)は、オペアンプの代わりに「Zero Cross Detector(ZCD)」を使ったパイプライン型A-D変換器の差動構成の回路図である。(b)はこのA-D変換器の動作タイミング図を示す。電荷転送フェーズではまず、プリチャージ信号φ2IがスイッチM3とM4±、M5±をオンに切り替えて、コンデンサC3±とC4±の充電状態を初期化する。次にφ2IがM4±とM5±をオフに切り替えると、電流源I2±とI3±、I4±がC3±とC4±を充電し始める。ZCDの差動入力端子の電位が一致(ゼロ交差)すると、ZCDの出力信号φ2eがM3をオフに切り替えて、コンデンサへの充電を停止し、次のステージで残留電荷のサンプリングを開始する。出典:米Massachusetts Institute of Technologyの発表資料90nmのCMOS技術で製造し、FOMは1変換当たり88fJ、占有面積は0.3mm2に抑えている。12ビット、50Mサンプル/秒級では、これまでに報告されているA-D変換器に比べて1/4程度の低電力化を実現した。

デジタル補正で低精度アナログを生かす

パイプライン型の高速化に関しては、米University of California, Los Angeles(UCLA)の成果に注目したい。10ビット分解能で500Mサンプル/秒の変換速度を達成した(講演番号は4.6)。高速化に向けてオペアンプの構成を最適化するとともに、デジタル方式の誤差補正技術を駆使して精度を確保した。

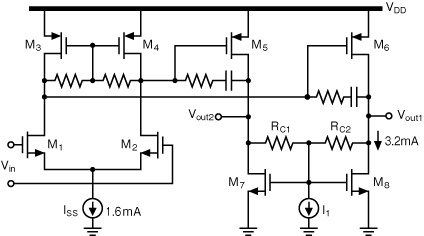

図2に同大学が用いたオペアンプを示す。一般に、低電源電圧で信号振幅を稼ぐには2段増幅回路を使う。さらに通常は、少しでも利得を稼ぐためにカスコード(縦積み)回路やゲイン・ブースト回路を付加する。しかし付加回路を使えば利得そのものは増大するが、利得帯域幅は狭くなってしまう。そこで同大学は、そのような付加回路を一切用いず、コモンモード・フィードバック回路も抵抗分圧器の中点電圧を用いる最も簡単なものとした。この結果、10GHzと広い利得帯域幅を確保できた。

図2 高速化に主眼を置いたオペアンプ回路 出力振幅を最大化するため、2段増幅回路の構成を採用した。ただし、利得は稼げるが利得帯域幅を狭めてしまうカスコード(縦積み)回路などは付加していない。さらに、信号経路には動作速度を制限する大型のトランジスタを利用しないようにした。こうして、10GHzと広い利得帯域幅を確保した。出典:米University of California, Los Angelesの発表資料

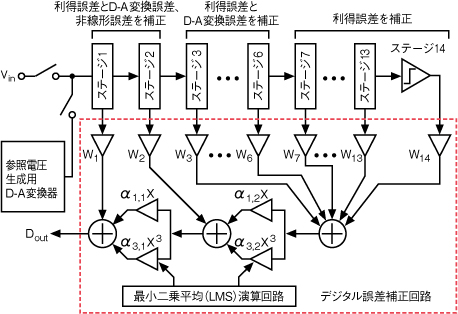

図2 高速化に主眼を置いたオペアンプ回路 出力振幅を最大化するため、2段増幅回路の構成を採用した。ただし、利得は稼げるが利得帯域幅を狭めてしまうカスコード(縦積み)回路などは付加していない。さらに、信号経路には動作速度を制限する大型のトランジスタを利用しないようにした。こうして、10GHzと広い利得帯域幅を確保した。出典:米University of California, Los Angelesの発表資料ただし利得はわずか30dB程度にとどまる。通常パイプライン型A-D変換器は、分解能をNとして6N+10dB以上の利得が必要だ。すなわち10ビット(N=10)の場合は、70dB以上なければ精度が出ない。30dBでは、分解能は3ビットが良いところである。そこで同大学は、このような低利得のオペアンプを用いても10ビット程度の精度が得られるように、デジタル誤差補正を導入した。図3にその構成を示す。破線で囲んだ部分がデジタル誤差補正回路で、今回はチップには集積せず、外付け回路として実現した。

図3 デジタル補正でオペアンプの利得を補う 1.5ビット冗長構成の単位A-D変換回路を13段、さらに1ビットの単位A-D変換回路を1段、パイプライン接続したA-D変換器である。デジタル方式の補正回路を使って、ステージ7〜14は利得誤差を補正し、ステージ3〜6ではさらにD-A変換誤差も、ステージ1と2ではさらに非線形誤差も補正する。出典:米University of California, Los Angelesの発表資料

図3 デジタル補正でオペアンプの利得を補う 1.5ビット冗長構成の単位A-D変換回路を13段、さらに1ビットの単位A-D変換回路を1段、パイプライン接続したA-D変換器である。デジタル方式の補正回路を使って、ステージ7〜14は利得誤差を補正し、ステージ3〜6ではさらにD-A変換誤差も、ステージ1と2ではさらに非線形誤差も補正する。出典:米University of California, Los Angelesの発表資料このデジタル誤差補正回路の動作を考察してみよう。パイプライン型で主流となっている1.5ビット冗長構成の単位A-D変換回路では、理想状態での入出力関係を以下のように表せる。

ここで、Voutは単位A-D変換回路のアナログ出力電圧、Vinは同アナログ入力電圧、Doutは同デジタル出力、Vrefは参照電圧である。式(1)は次のように変形できる。

実際の回路では、コンデンサの静電容量に不整合があったり、オペアンプの入出力特性に非線形性があったりする。これらを考慮すると、式(2)は次式で近似できる。

ここで、αは各ステージのアナログ入出力信号伝達関数の逆関数を近似する多項式の係数であり、α1,jが1次の項、α3,jが3次(歪み)の項、wjは各ステージの重み付け係数、添え字のjはパイプライン・ステージの段数である。

デジタル誤差補正回路は、参照電圧生成用D-A変換器の出力電圧を入力して、変換結果として得られたデジタル値と、参照電圧生成用D-A変換器に与えたデジタル値とを比較し、両者の差が最小になるようにα1,jとα3,j、wjそれぞれの値を設定する。この作業をパイプラインの後段から前段に向かって1段ずつ順番に実施していく。

この補正技術により、補正前は約40LSB(Least Significant Bit)だった誤差を1LSBまで低減した。90nmのCMOS技術で製造し、主な特性は、変換精度の指標となるSNDR(Signal to Noise and Distortion Ratio)が53dB、消費電力が55mW、FOMが1変換当たり310fJである。インターリーブを用いない10ビットA-D変換器としては、これまでに報告されている成果で最も高速・低電力である。

オペアンプを使わずに2倍増幅を実現

パイプライン型A-D変換器において、オペアンプは前段から受け取った電圧値を正確に2倍に増幅する役割を担う。ところが冒頭で述べたように、プロセス技術の微細化とともに演算精度が劣化し、大きな誤差を生じ始めている。そこでデジタル誤差補正を使って所要の精度を確保する手法が提案されているわけだが、「それならば、いっそオペアンプを使わずに2倍増幅を実現しよう」という発想が出てくる。それがカナダUniversity of TorontoとオランダBroadcom社が共同開発したパイプライン型A-D変換器だ(講演番号は9.2)。同じ充電状態のコンデンサを2個、直列に接続して2倍の電圧を取り出す手法を採る。

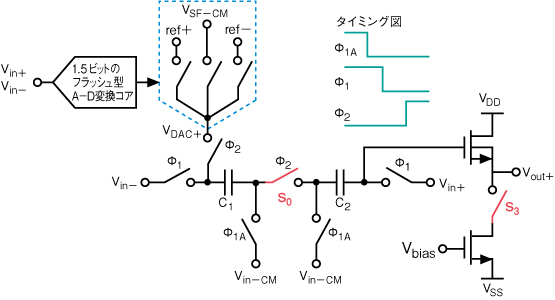

両者が開発した2倍増幅回路を図4に示す。コンデンサとスイッチを組み合わせたチャージ・ポンプ回路を使う。まず入力の差動信号(Vin+とVin−)を静電容量が同じコンデンサ(C1とC2)でそれぞれ標本化し、次にこれらのコンデンサを直列に接続すれば、約2倍の電圧を作り出せる。後はこれをソースフォロワ回路でバッファしてやれば良い。実際の増幅率は、寄生容量の存在により厳密に2倍とはならず、1.75倍程度になってしまうが、これについてはデジタル誤差補正回路で補償できる。これにより今回は、分解能が10ビットのときに、未補正では20LSB程度あった積分非直線性誤差(INL)が1LSB以下に抑えられた。

図4 チャージ・ポンプ利用の2倍増幅回路 1.5ビット冗長構成の単位A-D変換回路である。実際には差動構成だが、この図では正電圧側のみを示した。コンデンサとスイッチを組み合わせたチャージ・ポンプ回路が2倍増幅器として機能する。タイミング図のように各スイッチを切り替えることで、入力電圧(Vin±)とD-A変換器の出力電圧(VDAC±)の差分を2倍して取り出せる。これをソースフォロワ回路を介して後段に出力する。出典:カナダUniversity of TorontoとオランダBroadcom社の発表資料

図4 チャージ・ポンプ利用の2倍増幅回路 1.5ビット冗長構成の単位A-D変換回路である。実際には差動構成だが、この図では正電圧側のみを示した。コンデンサとスイッチを組み合わせたチャージ・ポンプ回路が2倍増幅器として機能する。タイミング図のように各スイッチを切り替えることで、入力電圧(Vin±)とD-A変換器の出力電圧(VDAC±)の差分を2倍して取り出せる。これをソースフォロワ回路を介して後段に出力する。出典:カナダUniversity of TorontoとオランダBroadcom社の発表資料製造技術は0.18μmのCMOS。SNDRは58.2dB、変換速度は50Mサンプル/秒、消費電力は9.9mW、FOMは1変換当たり300fJである。

参考文献

†1)松澤昭、「A-D変換器の新たな地平拓く、極限に迫る低消費技術が登場」、EE Times Japan、2008年3月号、No.33、pp.51〜55.

†2)松澤昭、「A-D変換器の注目論文を解説、各方式とも着実に進化」、EE Times Japan、2007年4月号、No.22、pp.47〜49.

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- Intelの最新AI戦略と製品 「AIが全てのタスクを引き継ぐ時代へ」

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ