微細化の限界に挑む、Siと新材料の融合で新たな展望も:プロセス技術(6/10 ページ)

第2部 新材料でばらつき耐性向上を実現

強誘電体と磁性体は、これまでも強誘電体を使った不揮発性メモリー「FeRAM:

Ferroelectric Random Access Memory」や、磁性体を使った不揮発性メモリー「MRAM:Magnetoresistive Random Access Memory」の材料として、活発に研究開発が進められてきた。

自然に正と負に分極し、この自発分極の方向を外部電界によって変えられるという強誘電体の現象は、1920年代に発見された。その後、強誘電体の物理的性質の理解や加工技術の開発が進み、1990年代にはFeRAMが市場に登場した。一方、磁性体をメモリーとして使う上での基本的な現象であるトンネル磁気抵抗(TMR:Tunnel Magnetoresistive)効果は、1975年に発見された。現在ではこの効果を利用したMRAMが製品化されている。

強誘電体と磁性体をロジック回路に導入する最近の研究動向は、両材料を不揮発性メモリーに使うこれまでの研究の流れとは異なる。内部の状態を外部から変えられるという強誘電体や磁性体の特徴を生かして、MOSFETのしきい値電圧(Vth)のばらつきの悪影響を抑えようというものだ。微細化をさらに進展させる上で障害となる要素を、新材料で乗り越えることを狙う。

強誘電体利用で電源を0.5Vへ

微細化を推し進めるには、スケーリング則に従って、LSIを構成するMOS FETの電源電圧を下げる必要がある。電源電圧を下げれば消費電力を削減できる。

しかし現実には、電源電圧を引き下げるのは、そう簡単ではない。まず、MOS FETのVthを下げ続けてきた結果、これ以上Vthを引き下げるのが難しくなっている。さらに、微細化に伴ってVthのばらつき幅が相対的に大きくなっていることが理由である。「電源電圧は、量産レベルで1.2V、研究開発レベルで1.0Vで止まっている状況だ」(東京大学大学院工学系研究科電気系工学専攻の准教授の竹内健氏)という。そのため、微細化に伴った消費電力の増大が大きな課題になっている。

このような状況の中、竹内氏の研究グループは、強誘電体材料をゲート電極に使ったSRAM(「強誘電体SRAMと呼ぶ」)を試作し(図1)、電源電圧(駆動電圧)を0.5Vにまで引き下げても、安定動作する見通しをつけた*1)。

図1 0.5V動作の強誘電体SRAM 試作した6トランジスタ型のSRAMセルである。ゲート部分に強誘電体を使った点が新しい。強誘電体膜を薄くすることで、分極方向が変わりやすくしている。出典:東京大学竹内研究室

図1 0.5V動作の強誘電体SRAM 試作した6トランジスタ型のSRAMセルである。ゲート部分に強誘電体を使った点が新しい。強誘電体膜を薄くすることで、分極方向が変わりやすくしている。出典:東京大学竹内研究室分極利用でしきい値電圧を制御

一般に、SRAMの電源電圧を下げると、SRAMを構成する複数のトランジスタ間で生じるVthのばらつきに耐えられなくなり、SRAMの動作が安定しなくなる。例えば、既存のSRAMは、電源電圧を0.5Vにまで下げると、もはや正常に動作しなくなる。

「High」と出力すべきときに、「Low」と出力してしまう可能性が高まる。SRAMを安定動作させるには、Vthのばらつきに耐えるようにしなければならない。これを、強誘電体を使うことで実現しようというのが基本的な考え方である。SRAMに強誘電体を使うと、データの書き込みや読み出しといった動作が安定するように、MOSFETのVthを動的に変えられる。

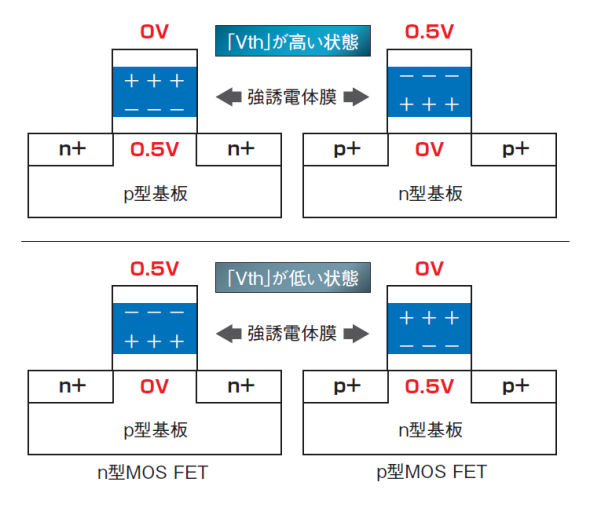

Vthが変わる原理はシンプルだ。例えば、n型MOS FETのゲート電極を0.5V(High)に設定すると、強誘電体中ではゲート電極側に負電荷が帯電し、一方のチャネル側には正電荷が帯電するように分極する。結果、チャネルには負電荷が引き寄せられ、Vthが0.1V程度下がる(図2)。

図2 強誘電体の分極変化でしきい値電圧が変わる 例えば、n 型MOSFETのゲート電極が0.5V(High)のとき(左下)、強誘電体中ではゲート電極側に負電荷が帯電し、一方のチャネル側には正電荷が帯電するように分極する。これによって、チャネルに電子が集まる。n型MOS FETのキャリアは電子なので、しきい値電圧Vthは低くなる。出典:東京大学竹内研究室

図2 強誘電体の分極変化でしきい値電圧が変わる 例えば、n 型MOSFETのゲート電極が0.5V(High)のとき(左下)、強誘電体中ではゲート電極側に負電荷が帯電し、一方のチャネル側には正電荷が帯電するように分極する。これによって、チャネルに電子が集まる。n型MOS FETのキャリアは電子なので、しきい値電圧Vthは低くなる。出典:東京大学竹内研究室このような強誘電体の動作によって、MOS FETがオンに入ろうとするときにはVthが下がってオン状態に入りやすくなり、オフのときにはVthが上がってオフ状態を保持しやすくなる(図3)。「単純な構造だけれど、SRAMの動作を安定させるように、すべてのつじつまが合っている」(竹内氏)という。

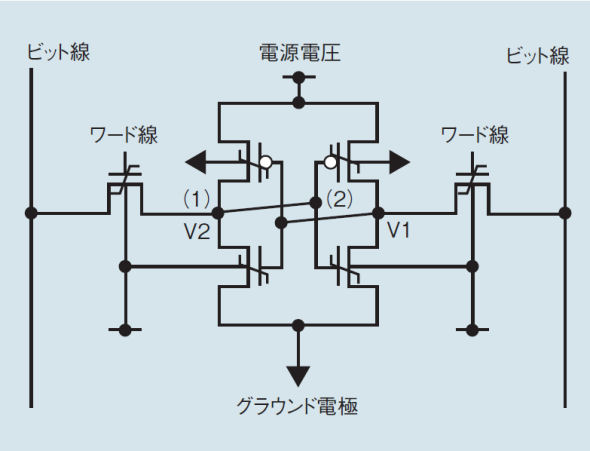

図3 強誘電体SRAMのデータが「0」のときの動作 初期状態は、V2が「0.5V」、V1が「0V」である。図3の(1)のポイントが0.5Vなので、V2と接続した図3の(2)のポイントも0.5Vになり、右下のn型MOS FETと、右上のp型MOS FETのゲート電極が0.5Vになる。右下のn 型MOS FETはゲート電圧が0.5V(high)なのでオン状態になり、このとき図2に示した通り、n型MOS FETのしきい値電圧は下がりオン状態の安定度が増す。右上のp型MOSのゲート電圧は0.5Vで、Vthが高まりオフ状態の安定度が増す。出典:東京大学竹内研究室

図3 強誘電体SRAMのデータが「0」のときの動作 初期状態は、V2が「0.5V」、V1が「0V」である。図3の(1)のポイントが0.5Vなので、V2と接続した図3の(2)のポイントも0.5Vになり、右下のn型MOS FETと、右上のp型MOS FETのゲート電極が0.5Vになる。右下のn 型MOS FETはゲート電圧が0.5V(high)なのでオン状態になり、このとき図2に示した通り、n型MOS FETのしきい値電圧は下がりオン状態の安定度が増す。右上のp型MOSのゲート電圧は0.5Vで、Vthが高まりオフ状態の安定度が増す。出典:東京大学竹内研究室これまで、基板のバイアス電圧を変えることで、基板上のMOS FETのVthを変える試みはあった。ただ今回のように、MOS FETのそれぞれのVth値が変わるデバイスは、従来のSi材料のみを使ったMOS FETでは現実的ではなかった。強誘電体という新材料を使ったからこそ、なしえたことである。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 重量はクジラ級! 超巨大な高NA EUV装置の設置をIntelが公開

- どうする? EVバッテリー リサイクルは難しい、でもリユースにも疑問

- 「GPT-4」を上回る性能で、グラフィカルな文書を読解するLLM技術

- 2023年の世界半導体売上高ランキングトップ20、NVIDIAが初の2位に

- 中国政府の「Intel/AMD禁止令」、中国企業への強い追い風に

- パワー半導体向けウエハー市場、2035年に1兆円台へ

- Intelが高NA EUV装置の組み立てを完了、Intel 14Aからの導入に向けて前進

- Intelの最新AI戦略と製品 「AIが全てのタスクを引き継ぐ時代へ」

- TSMC、24年Q1は増収増益 地震の影響は「最小限にとどまる」

- JDI、次世代有機ELディスプレイ「eLEAP」を24年12月に量産開始へ