「ムーアの法則を進める必要がある」――ARM:「IEDM 2015」基調講演で(2/2 ページ)

リソグラフィ技術の展望は?

また同氏は、次のように付け加えた。「より微細なパターンを描くためには、リソグラフィ装置を用いた複数の手法を採用しなければならないため、コストが増大する。しかし、7nmプロセス向けに開発予定のステッパーは、28nmプロセス用のものと比べて50%の高速化を実現することができるという。さらに、マスク業界は引き続き、書き込み時間にかかるコストを主に削減していくとともに、マルチ電子ビーム描画装置のコスト規模を大幅に削減するための取り組みを大きく前進させていくと宣言している」。

Yeric氏は、EUV(極端紫外線)リソグラフィ装置について懐疑的な見方をしているようだ。EUV装置はこれまで長期にわたり、より微細なパターンの描画を実現できる手段として最も期待されてきたが、仮にそうだとしても、あまりに課題が多すぎて、7nmプロセスに適用することができない可能性があるためだという。

同氏は、「EUVでは、7nmプロセス以降、マルチパターニングが必要になる。このため、5nmプロセス以降、リソグラフィ装置によってどれくらいのコスト削減が可能になるのかは不明だ。今のところ、EUVの代替としては、DSA(Directed Self-Assembly:誘導自己組織化)が最も有力とされている。しかしDSAにも、誘導パターンに限りがあるという独特の制約があるため、形成できる最終パターンが制限される可能性がある」と説明する。

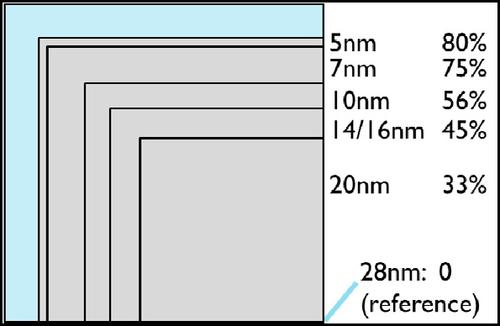

さまざまな課題の中でも特に重要なのが、性能を上回る電力を提供可能なトランジスタを搭載したチップを実現することは可能なのかという点だ。

「ダークシリコン(シリコンダイの中で電源をオフにするエリア)の問題を解決するには、寄生容量やオンチップワイヤの微細化などに対応するために、飛躍的な進歩を遂げる必要がある。例えば、多層グラフェンを用いたインターコネクトや、カーボンナノチューブバイアスなどの実現が挙げられる。16/14nmプロセス以降は、電力と性能の半分がワイヤ上で失われる可能性があるが、これについてはほんの数世代前まで、大した問題ではないとされていた」(同氏)。

NTCに注目集まる

Yeric氏は、将来性のある分野を幾つか挙げている。例えば、現在進められている、電力効率の最適化に向けた専用のコンピューティングブロックもその1つだ。

同氏は、「最終的に、GPUや画像認識用プロセッサなどは、ほぼコンピューティングに近い状態にまで進化するかもしれない。また、分類機能や整合機能など、インメモリの共通機能によるサポートを受けることによって、さらなる高効率化を実現し、完全なPIM(Processor In Memory)へと進化していく可能性もある」と述べる。

「さらに、ディープニューラルネットワークを利用すれば、ブロックを作成できる可能性もある。しかし、このようにプロセッシングとメモリを融合するには、論理/メモリチップに関する既存のさまざまな設計/製造手法を変化させる必要がある」(Yeric氏)。

現在成長が見込まれているIoT用超低消費電力デバイスに向けた、NTC(Near-Threshold Computing)の研究に期待が寄せられているようだ。IoTシステムは、消費電力量を最小化するために、ノーマリーオフ型のコンピューティングを採用する一方で、ユースケースでは常時オンのセンシングを必要とすることから、NTCには二重のメリットがあることが実証されているためだ。Yeric氏は、NTCの技術は、RFアナログICでの採用が適しているとみている。

【翻訳:田中留美、編集:EE Times Japan】

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- パワー半導体受託生産のJSファンダリが破産申請、負債総額約161億円

- Qualcommの狙いは何なのか、やたらと「高い」Alphawave買収額

- 25年5月の世界半導体市場は全地域で成長、19.8%増の590億ドルに

- 危うい再建計画 Wolfspeed、CHIPS法補助金で再生図るか

- 22nmプロセス採用でMRAM内蔵、ルネサスがエッジAI特化の新マイコン

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- データセンター向けAI半導体のEsperantoが事業縮小、技術売却を模索

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

- 半導体製造ラインの立ち上げ迅速に、日本IBMが京都に開発拠点

チップにおけるダークシリコンの割合は、何らかの新しい技術を導入しなければ、増えていく一方だ 出典:ARM

チップにおけるダークシリコンの割合は、何らかの新しい技術を導入しなければ、増えていく一方だ 出典:ARM 出典:IEDM

出典:IEDM ARMから見た7nm CMOS時代のCPU設計(1)

ARMから見た7nm CMOS時代のCPU設計(1) ナノワイヤと非シリコン材料で「ムーアの限界」を突破

ナノワイヤと非シリコン材料で「ムーアの限界」を突破 東芝 大分300mmラインのソニーへの譲渡正式合意

東芝 大分300mmラインのソニーへの譲渡正式合意 LEDを一新した「GaN」、次は電力を変える

LEDを一新した「GaN」、次は電力を変える