IEDMで発表されていた3D XPointの基本技術(前編):福田昭のデバイス通信(60)(1/2 ページ)

米国で開催された「ISS(Industry Strategy Symposium)」において、IntelとMicron Technologyが共同開発した次世代メモリ技術「3D XPoint」の要素技術の一部が明らかになった。カルコゲナイド材料と「Ovonyx」のスイッチを使用しているというのである。この2つについては、長い研究開発の歴史がある。前後編の2回に分けて、これらの要素技術について解説しよう。

3D XPointの要素技術が一部明らかに

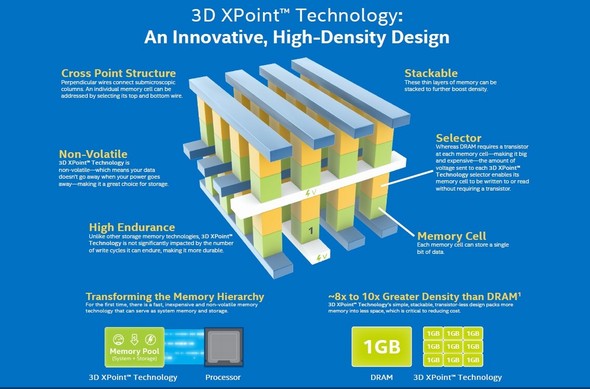

謎に包まれていた次世代メモリ技術「3D XPoint(スリーディー・クロスポイント)」の要素技術が一部、明らかになった。3D XPointメモリは、IntelとMicron Technologyが共同開発し、両社が2015年7月29日(米国時間)に大々的に発表した次世代の不揮発性メモリである*)。DRAMに比べて10倍も記憶密度が高く、NANDフラッシュメモリに比べて1000倍もアクセスが速く、NANDフラッシュメモリの1000倍の書き換え寿命を有すると喧伝(けんでん)された。

*)関連記事:IntelとMicronの新不揮発メモリ「3D XPoint」

華々しく発表されたにもかかわらず、3D XPointのメモリ技術は具体的な記述が避けられていた。分かっているのは、2層のクロスポイント・メモリであることと、記憶容量が128Gbitと大容量であること(つまり1層当たり64Gbitであること)くらい。次世代不揮発性メモリの研究開発コミュニティーでは、2層のクロスポイント構造は特に珍しくはない。さすがに128Gbitもの大容量チップを開発した事例は学会で公表されていないものの、2層のクロスポイント構造で32Gbitの大容量チップ(抵抗変化メモリ)はSanDiskと東芝が共同で試作し、国際学会ISSCCで2013年2月に発表済みである。

3D XPointメモリは報道機関向けの説明会や説明動画の公表などはなされたものの、2016年1月の時点では、技術内容が国際学会で発表された形跡は見当たらない。その実現技術はベールに包まれていた。

そんな中で、半導体製造装置と半導体材料の業界団体SEMIが2016年1月10日~13日に米国カリフォルニア州のベイエリア(サンフランシスコとシリコンバレーの中間点)で開催した有償の業界イベントISS(Industry Strategy Symposium)で、1月12日にIntelとMicronの合弁によるNANDフラッシュメモリの開発製造企業IM Flash Technologiesが3D XPointメモリの要素技術を一部、明らかにした。発表者は同社の共同CEOをつとめるGuy Blalock氏である。Blalock氏の講演概要は、本誌が報告済みだ*)。

*)関連記事:3D XPoint、開発から製造へ

Blalock氏の講演で最も重要なポイントは、メモリセルの要素技術が示されたことだろう。本誌の既報によると「3D XPoint技術は、カルコゲナイド材料と『Ovonyx』のスイッチを使用している」とある。ここから、記憶素子はカルコゲナイド材料、セル選択素子はOvonic(オボニック)スイッチであることが分かる。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -- EE Times Japanテ勇DN Japan 邨ア蜷磯崕蟄千沿�壼刈騾溘☆繧九後ぎ繝ゥ繧ケ蝓コ譚ソ縲埼幕逋コ縲譌・譛ャ繧ゅ¢繧灘シ募スケ縺ォ窶補� 髮サ蟄千沿2025蟷エ4譛亥捷

- 髢狗匱繧堤ー。邏�蛹悶@遶カ莠牙鴨繧貞シキ蛹悶☆繧九∫ャャ4荳紋サ」豎守畑USB繝�ヰ繧、繧ケ繧ウ繝ウ繝医Ο繝シ繝ゥ繝シ縺ョ螳溷鴨

- 蜊雁ー惹ス謎ク崎憶隗」譫舌�譁ー蠅�慍縲√�繝ュ繧サ繧ケ髢狗匱繧貞刈騾溘☆繧区ャ。荳紋サ」縺ョ3D X邱夐。募セョ髀。縺ョ螳溷鴨

- 縲悟屓謚倥さ繝ウ繝医Λ繧ケ繝医ヨ繝「繧ー繝ゥ繝輔ぅ縲阪r遐皮ゥカ螳、繝ャ繝吶Ν縺ァ螳溽樟縺吶k譁ケ豕輔→縺ッ��

- 蜊雁ー惹ス灘膚遉セ 讌ュ邵セ縺セ縺ィ繧√�2025蟷エ3譛域悄隨ャ3蝗帛濠譛溘�

Special Contents 2

- PR -記事ランキング

- 半導体メーカーの「悲喜こもごも」 絶好調のTSMC、人員削減のST

- IntelがAltera売却へ、株式51%を米投資ファンドに

- 2024年の半導体市場は21%成長 NVIDIAが初の首位に

- ミネベアミツミが芝浦電子買収へ 「8本槍」戦略強化に向け

- 2035年のウエハー需要を予測する ~半導体も「VUCA時代」に

- 1インチサイズの全固体電池を10秒で作製 レーザーで加工

- AIのデータ転送問題解決に王手、シリコンフォトニクス新興企業

- トランプ政権の「アメとムチ」 Intelは補助金を受け取れるのか

- チップに「水路」を作り冷却液を流し込む 高効率に放熱

- 世界半導体市場が10カ月連続で17%以上成長 2月として過去最高に