IEDMで発表されていた3D Xpointの基本技術(後編):福田昭のデバイス通信(61)(1/2 ページ)

前編に続き、IntelとMicron Technologyの次世代不揮発性メモリ「3D XPoint」について解説しよう。今回は、「オボニック・スレッショルド・スイッチ(OTS:Ovonic Threshold Switch)」と、材料について詳しく見ていきたい。

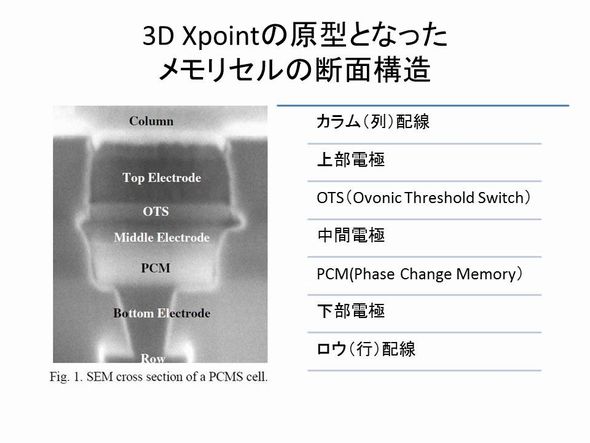

PCMとOTSの直列接続でセルを構成

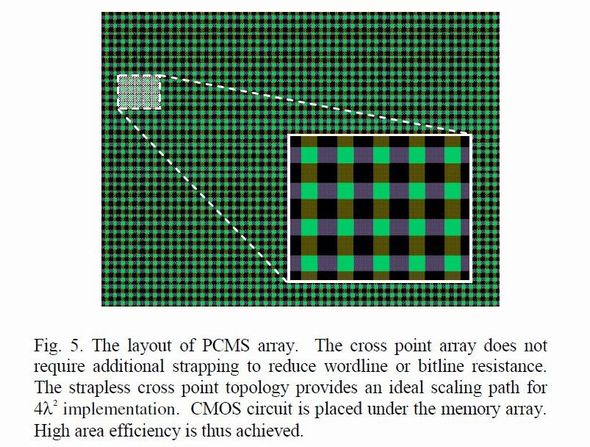

前編でご説明したように、IntelとMicron Technologyが共同開発中の次世代不揮発性メモリ「3D Xpoint(スリーディー・クロスポイント)」は、2009年に国際学会IEDM(IEDM 2009)でそのひな型となる技術が公表されていた(講演番号27.1)。1層のクロスポイント構造で記憶容量が64Mbitの不揮発性メモリ技術を、IntelとNumonyx(現在はMicron)の共同開発チームが発表していた。

IEDM 2009で発表された不揮発性メモリは、記憶素子が相変化メモリ(PCM:Phase Change Memory)、セル選択素子が「オボニック・スレッショルド・スイッチ(OTS:Ovonic Threshold Switch)」である。

PCMは、カルコゲナイド材料が電圧印加によって合金状態(低抵抗状態)とアモルファス状態(高抵抗状態)のどちらかの状態となり、電圧印加をやめてもその状態を維持する性質(不揮発性)を利用する。ちなみに低抵抗状態をLRS、低抵抗状態にすることをセット(SET)、高抵抗状態をHRS、高抵抗状態にすることをリセット(RESET)と呼ぶことが多い。

OTSは、カルコゲナイド材料の相変化とは少し違った性質を利用する。材料は、初期状態が高抵抗状態(オフ状態、かつアモルファス状態)にある。ここで外部から印加する電圧を徐々に上げていくと、ある電圧(スレッショルド電圧)で突然、低抵抗状態(オン状態、かつ合金状態)に以降し、電流が一気に流れ出す。印加電圧をゼロにすると、材料は再び高抵抗状態(オフ状態)に戻る。カルコゲナイド材料の備えるこのような性質をスイッチ素子に利用したのが、OTSである。

1個のメモリセルは、1個のPCM素子と1個のOTS素子を直列に接続した積層構造になる。この構造を共同開発チームは、「PCMS」(PCMプラスOTSの意味)と呼んでいた。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -スポンサーからのお知らせ

- PR -Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- 世界半導体製造装置市場、2026年は過去最高に

- 2025年は数年に一度の「ビッグチェンジ」イヤー、NVIDIAとAMDの最新GPUを分解

- GaN撤退のTSMC、その後の戦略を考察する

- ついにできた!Rapidus試作ライン稼働、2nm GAAトランジスタの動作を確認

- 「過去の投資は過剰だった」 Intel、ドイツとポーランドの新工場計画を中止

- STがNXPのMEMSセンサー事業買収へ、最大9億5000万ドルで

- ルネサス、Wolfspeed再建支援で25年上期は1753億円の赤字

- ウシオ電機、オスラムグループのランプ事業を買収

- 第9世代BiCS FLASH適用512Gb TLC製品、キオクシアがサンプル出荷

- パワー半導体受託生産のJSファンダリが破産申請、負債総額約161億円