3D NANDフラッシュメモリの断面構造と製造工程:福田昭のストレージ通信(116) 3D NANDのスケーリング(4)(2/2 ページ)

3D NANDフラッシュのメモリセルアレイ製造工程

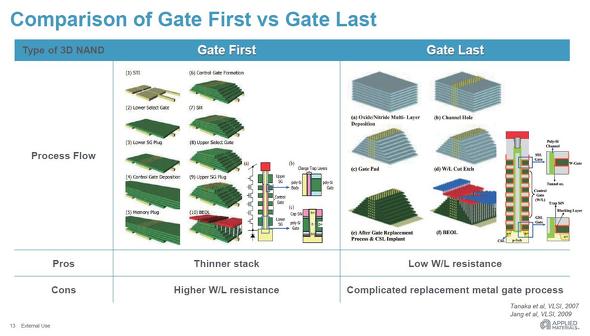

このような新しくて非常に複雑な構造のメモリセルアレイを製造するためには、工程数をいくらかでも少なくすることで製造コストを下げる技術が求められる。代表的な製造工程は、東芝が開発した「ゲートファースト」と呼ばれる技術と、Samsung Electronicsが開発した「ゲートラスト」と呼ばれる技術である。

「ゲートファースト」技術では、多結晶シリコン膜(制御ゲート)の層と絶縁膜の層を交互に積み重ねてから、積み重ねた層を貫通する細長い孔を千鳥格子状に空ける。この膨大な数の細長い孔(メモリホール)をわずか1回のエッチングによって空けることが、製造コストの大幅な削減に寄与している。次に、メモリホールの側壁に電荷捕獲用の窒化膜を形成する。そして多結晶シリコン(チャンネル)でメモリホールを埋める。それから制御ゲート層を階段状にエッチングし、金属配線工程(BEOL:Back End Of Line)へと移行する。

「ゲートラスト」技術では、シリコン酸化膜とシリコン窒化膜を交互に積み重ねてから、積み重ねた層を貫通する細長い孔(チャンネルホール)を千鳥格子状に空ける。そして孔(チャンネルホール)を多結晶シリコンで埋めてチャンネルとする。続いてステアケース領域を階段状に加工する。それからチャンネルの間に、積み重ねた層を貫通する細長い溝を形成する。細長い溝の側壁を通じてシリコン窒化膜の層を取り除き、側壁に電荷捕獲用の窒化膜を形成する。そして側壁の溝(最初のシリコン窒化膜を除去してできた溝)にタングステン金属を埋めて制御ゲートとする。それから余分のタングステン金属を取り除き、金属配線工程(BEOL)へと移行する。

「ゲートファースト」技術の利点は、製造工程のステップ数が少ないことと、積み重ねる層(ペア層)を薄くできることである。弱点は、制御ゲート(ワード線)の材料が多結晶シリコンであるために電気抵抗があまり低くならないことだ。「ゲートラスト」技術の利点は、制御ゲート(ワード線)の材料がタングステン金属なので電気抵抗が低くなることである。弱点は、製造工程のステップ数が多くなるとともに製造が複雑になることだ。

(次回へ続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -- EE Times Japanテ勇DN Japan 邨ア蜷磯崕蟄千沿�� 蜊雁ー惹ス捺・ュ逡� 縺薙l縺セ縺ァ縺ョ20蟷エ縲√%繧後°繧峨�20蟷エ窶補� 髮サ蟄千沿2025蟷エ6譛亥捷

- 繧「繝励Μ繧ア繝シ繧キ繝ァ繝ウ縺ョ隕∽サカ縺ォ蠢懊§縲√す繧ー繝翫Ν繝√ぉ繝シ繝ウ縺ョ豸郁イサ髮サ蜉帙r蜑頑ク帙☆繧区婿豕�

- 菴取カ郁イサ髮サ蜉幢シ城ォ倡イセ蠎ヲ縺ョ繧キ繧ー繝翫Ν繝√ぉ繝シ繝ウ縲∵ウィ諢上r謇輔≧縺ケ縺阪ち繧、繝溘Φ繧ー隕∝屏縺ィ縺ッ��

- 譛ャ迚ゥ縺ィ隕句�縺代′縺、縺九↑縺�キァ螯吶↑蛛ス騾�蜊雁ー惹ス楢」ス蜩√∽シ∵・ュ縺瑚ェソ驕斐〒豌励r莉倥¢繧九%縺ィ縺ッ��

- Intel縲∽サ翫←縺�↑縺」縺ヲ繧具シ溘闍ヲ蠅�r謚懊¢蜃コ縺帙k縺�

Special Contents 1

- PR -記事ランキング

- DRAM業界をかき乱す中国勢、DDR4の供給の行方は?

- 微細化前倒しや3層積層の強化……「市場で勝ち切る」ソニーの半導体戦略

- センサーで微細プロセス、ロジックも12nm導入へ ソニーのイメージセンサー戦略

- AMDがAI新興Untether AIのエンジニアチーム「だけ」買収

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- ロームとNVIDIA、AIファクトリー実現に向け協業

- 自動運転のキーデバイスとなる車載SoC

- ルネサスがWolfspeedの再建支援、Q2には2500億円の減損か

- 全固体電池向けの固体電解質市場、2030年以降に急加速か

- キオクシアが攻める「NANDとDRAMのあいだ」 NVIDIAと協業も

3次元集積化(3D IC)の理想と現実

3次元集積化(3D IC)の理想と現実 モバイル端末向けパッケージング技術「FOWLP」(前編)

モバイル端末向けパッケージング技術「FOWLP」(前編) 膨張を続けるデジタルデータをNANDフラッシュが貯蔵

膨張を続けるデジタルデータをNANDフラッシュが貯蔵 NANDフラッシュの基本動作(前編)

NANDフラッシュの基本動作(前編) 「SSDが壊れる」まで(前編)

「SSDが壊れる」まで(前編) DRAMについて知っておくべき、4つのこと

DRAMについて知っておくべき、4つのこと