ルネサス、SOTBプロセス用低電力フラッシュ技術:読み出しエネルギーは0.22pJ/b

ルネサス エレクトロニクスは、65nmのSOTB(Silicon On Thin Buried Oxide)プロセスに混載可能なフラッシュメモリの低消費電力化技術を開発した。

環境発電専用の組み込みコントローラICに採用

ルネサス エレクトロニクスは2019年6月、65nmのSOTB(Silicon On Thin Buried Oxide)プロセスに混載可能なフラッシュメモリの低消費電力化技術を開発したと発表した。

SOTBプロセス技術は、動作時と待機時の消費電力をいずれも小さくできる技術である。この技術は既に、エナジーハーベスト(環境発電)専用の組み込みコントローラIC「R7F0E」に採用されている。

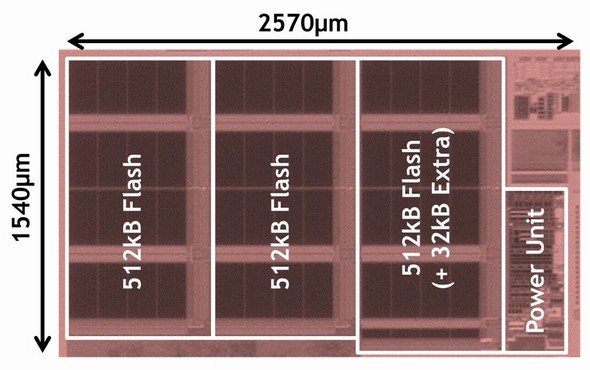

今回は、このSOTBプロセスに混載可能な低消費電力の「2T-MONOS(2 Transistors-Metal Oxide Nitride Oxide Silicon)」フラッシュメモリを開発した。2トランジスター構造にしたことで、従来の1トランジスター構造で必要だった読み出し時の負電圧が不要となり、読み出し動作の電力消費を抑えることができた。

しかも、MONOSは他のメモリプロセスに比べ、少ないマスク枚数で製造することができ、製造コストを低減できる。また、離散的にデータ記憶が可能なことから、データの書き換え動作について、高い信頼性を実現できるという。

メモリの読み出し動作についても、消費電力を低減する工夫を行った。その1つはメモリデータを判定するセンス動作である。ビット線プリチャージエネルギーを削減するシングルエンド型センスアンプに、新たな電荷転送方式を採用した。これにより、プリチャージ速度とエネルギー効率を改善した。もう1つは、センスアンプ用のレファレンス電圧を最適化するレギュレーター回路技術である。これらの技術により、センス動作の高速化と消費電力の低減を可能とした。

データ転送エネルギーを削減できる回路技術も開発した。トランジスターしきい値(Vth)が小さいというSOTBプロセスの特長を生かし、データ転送時の電圧振幅を抑えた。これにより、データを外部に転送する時の転送エネルギーを削減できたという。

R7F0Eは、メモリ読み出し電流がわずか6μA/MHzである。この数値はマイコン内蔵フラッシュメモリとして、0.22pJ/ビット(動作周波数64MHz)の読み出しエネルギーに相当する。動作時の消費電流は20μA/MHzである。これに対してSOTBを用いない2T-MONOSフラッシュメモリは、読み出し電流として約50μA/MHzが必要になるという。

今回の研究成果は、京都で開催中の「2019 VLSI技術/回路シンポジウム(2019 Symposia on VLSI Technology and Circuits)」(2019年6月9~14日)で詳細を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -記事ランキング

- Xiaomi 15S Proを分解、10年かけて磨き続けた半導体開発力

- 半導体のネガティブイメージ解消へ、ソニーやキオクシアら国内大手が集結

- 中国半導体装置展示会「CSEAC」レポート 中工程シフトと“露光回避”の実態

- 「充電5分で520km走行」を巡る疑問、 中国CATLの車載バッテリー発表を考察

- 創刊前の20年間(1985年~2005年)で最も驚いたこと:「高輝度青色発光ダイオード」(前編)

- 「鉄とマンガン」が半導体の微細化を進化させる?

- 「CEATEC 2025」ことしも10万人超えへ 吉村知事が万博語るセッションも

- TO-247より省面積、ロームの新SiCパワーモジュール

- STがパネルレベルパッケージの試作ライン新設へ 6000万ドル投じ

- SiFiveの新RISC-VコアはAI特化 メモリ管理の革新で性能向上

2T-MONOSフラッシュメモリのブロック図 出典:ルネサス

2T-MONOSフラッシュメモリのブロック図 出典:ルネサス 組み込みAIを加速する、ルネサスの新Processing-in-Memory

組み込みAIを加速する、ルネサスの新Processing-in-Memory ルネサス、高精度AFEとマイコンを1チップに集積

ルネサス、高精度AFEとマイコンを1チップに集積 ルネサス、仮想化を実現する車載制御マイコン

ルネサス、仮想化を実現する車載制御マイコン 環境発電で“欠けていたピース”埋める、ルネサスのSOTB

環境発電で“欠けていたピース”埋める、ルネサスのSOTB ルネサス、統合コックピット向け開発評価キット発売

ルネサス、統合コックピット向け開発評価キット発売 ルネサス、非接触UIソリューションの供給を開始

ルネサス、非接触UIソリューションの供給を開始