次々世代の不揮発性メモリ技術「カーボンナノチューブメモリ(NRAM)」:福田昭のストレージ通信(153) 半導体メモリの技術動向を総ざらい(14)(2/2 ページ)

開発企業Nanteroは共同開発や技術ライセンスなどでビジネスを展開

Nanteroは自社で不揮発性メモリ製品を開発しない。ビジネスの基本的な考え方は共同開発や技術ライセンスなどである(参考記事:「NRAMの早期実用化を目指す、Nanteroが資金集めを加速」)。最近の開発動向を以下に示そう。

中央大学は2014年6月にNanteroと共同で、140nm世代の製造技術によるNRAM記憶素子を試作し、20nsと短い電圧パルスによってデータを書き換えられることや、1000億回の書き換え寿命があることなどを確認した(参考記事:「カーボンナノチューブを使った「NRAM」の基本動作を実証」。

富士通セミコンダクターと三重富士通セミコンダクターは2016年8月に、NanteroとNRAM技術による半導体製品の共同開発で合意したと発表した(参考記事:「富士通セミ、CNT応用メモリ「NRAM」を商品化へ」)。55nm世代の製造技術によってNRAM混載カスタムLSIや単体NRAMなどを共同開発する。発表当時のニュースリリースでは製品化予定を2018年末としていたが、2019年6月中旬の時点では、製品はリリースされていないようだ。

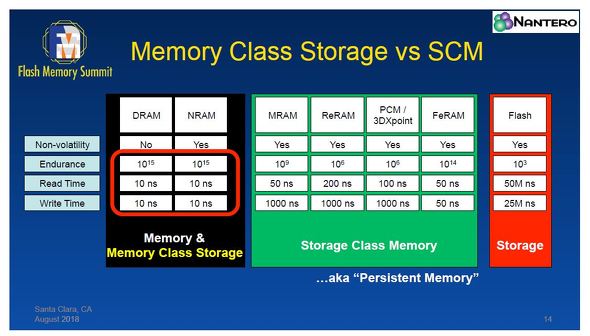

またNanteroは2018年8月に半導体に関する複数のイベントで、「大容量NRAMによって主記憶のDRAMを置き換える」アイデアを発表した。28nm世代の製造技術によって4GビットのNRAMシリコンダイを始めに開発する。メモリセルは1個のトランジスタと1個のCNT記憶素子で構成する。

続いて製造技術を14nm世代に微細化したNRAMを開発する。シリコンダイ当たりの記憶容量は4倍の16Gビットになるとする。これは現在のDRAMシリコンダイの最大容量に匹敵する。製造技術を7nm世代とさらに微細化すると、シリコンダイ当たりで64Gビットの大容量不揮発性メモリを実現できるとNanteroは主張する。

さらに、3次元クロスポイント構造を採用して記憶容量を拡大するNRAMのアイデアについてもNanteroは発表している。ただし、クロスポイント構造で必須とされる、セレクタの技術についてはふれていない。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 1

- PR -Special Contents 2

- PR -記事ランキング

- 講演会場が静まり返った――中国が生み出した衝撃のトランジスタ構造

- 「DRAM生産の4割を米国で」 Micronを待ち受ける過酷な競争

- TSMCがGaN事業撤退へ、ロームは「さまざまな可能性を協議」

- TSMCがGaNファウンドリー事業から撤退へ、NavitasはPSMCと提携で対応

- 25年Q1のファウンドリー市場は縮小緩やかも、Samsung/GFは大幅低迷

- 最大の壁、p層を克服!酸化ガリウムでFLOSFIAが達成した「世界初」

- 加速器を用いた「省電力次世代EUV露光技術」開発へ

- 「光で剥離」 次世代半導体パッケージの歩留まりと生産性向上へ

- SoC設計期間を「10分未満」に短縮 インドRISC-V新興

- 26年度には世界大手の9割が採用、黒字化も 本格化するソニーの車載イメージセンサー

DRAM価格、2019年に40%下落と予測、Yole

DRAM価格、2019年に40%下落と予測、Yole 一度消えたPCMが「3D XPointメモリ」で劇的にカムバック

一度消えたPCMが「3D XPointメモリ」で劇的にカムバック 「3D XPointメモリ」開発のオープン・モードとステルス・モード

「3D XPointメモリ」開発のオープン・モードとステルス・モード 磁気抵抗メモリ(MRAM)の長所と短所

磁気抵抗メモリ(MRAM)の長所と短所 メモリ不況の夜明けは近い、市場動向から見たDRAMとNANDの挙動

メモリ不況の夜明けは近い、市場動向から見たDRAMとNANDの挙動 Micron広島工場の新棟が完成、1Y/1Znm生産加速

Micron広島工場の新棟が完成、1Y/1Znm生産加速