次世代コンデンサの主役を狙うシリコンキャパシタ:福田昭のデバイス通信(227) 2019年度版実装技術ロードマップ(37)(1/2 ページ)

今回は、次世代のコンデンサである「シリコンキャパシタ(シリコンコンデンサ)」を解説する。

高い耐熱性と優れた温度特性、高い容量密度が特長

電子情報技術産業協会(JEITA)が発行した「2019年度版 実装技術ロードマップ」に関する完成報告会(2019年6月4日に東京で開催)と同ロードマップの概要をシリーズでご報告している。今回はその第37回である。

本シリーズの第31回から、第4章「電子部品」の概要を説明してきた。第4章「電子部品」は、「4.1 LCR部品」、「4.2 EMC対策部品」、「4.3 センサ」、「4.4 コネクタ」、「4.5 入出力デバイス」の5つの節に分かれる。第33回からは「4.1 LCR部品」の第2項「4.1.2 コンデンサ」の概要をご紹介している。第33回は全体像、第34回は「積層セラミックコンデンサ(MLCC:Multi-Layer Ceramic Capacitors)」、第35回は「フィルムコンデンサ」、第36回(前回)は「アルミ電解コンデンサ」の概要をご説明した。いずれも代表的なコンデンサである。今回は、次世代のコンデンサである「シリコンキャパシタ(シリコンコンデンサ)」を解説する。

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第31回から、第4章「電子部品」(プログラムの8番)の概要を紹介している (クリックで拡大)出典:JEITA

2019年6月4日に東京で開催された「2019年度版 実装技術ロードマップ」完成報告会のプログラム。本シリーズの第31回から、第4章「電子部品」(プログラムの8番)の概要を紹介している (クリックで拡大)出典:JEITAシリコン半導体プロセスで作るコンデンサ

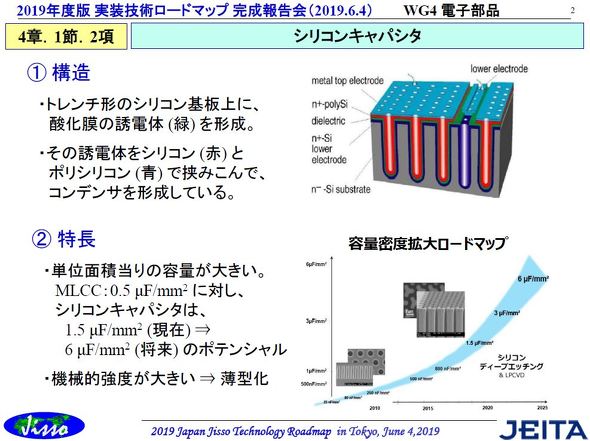

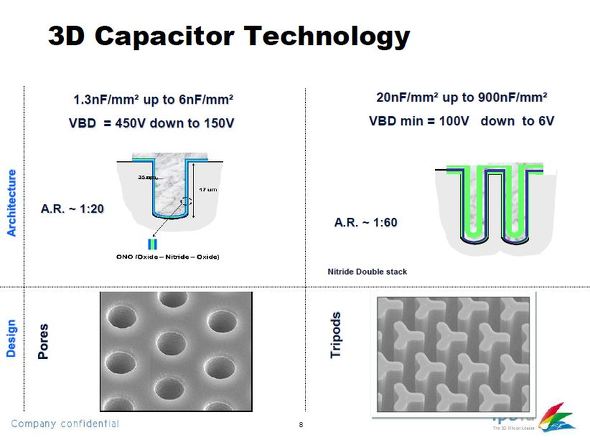

「シリコンキャパシタ(シリコンコンデンサ)」は、シリコン半導体プロセスによって製造する。シリコンウエハー(シリコン基板)にエッチングによって深い溝を作って多結晶シリコンと誘電体、単結晶シリコンの3層構造によるキャパシタを作成し、基板の上面と下面に電極を形成する。DRAMの溝型キャパシタと似ている。ただし実際には溝型キャパシタのような比較的簡素な円筒形の孔ではなく、「トライポッドピラー(Tripod Pillar)」と呼ぶ3方向(120度ずつ異なる方向)に側面が飛び出した柱を形成することによって単位面積当たりの静電容量を大幅に増やしている。

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents

- PR -Special Contents 2

- PR -記事ランキング

- ソニーが「最速」のSPAD距離センサー開発、自動運転L3以上へ

- 「NVIDIAと真逆の取り組みをしよう」 Jim Keller氏

- JDIの液晶の知見、先端半導体パッケージングの中核技術に

- 「本当に安全なのか」 中国の機器や部品を見直すべき

- キオクシアの年度業績、3年ぶりの黒字転換で過去2番目の営業利益を計上

- 半導体市場25年は予想以上に伸びるが26年はメモリが失速? ―― WSTS春季予測考察

- キオクシアのNAND戦略 「BiCS FLASH」はどう進化するのか

- イメージセンサー金額シェア60%目標「数年遅れる」、ソニー半導体

- 世界半導体市場は12カ月連続で成長、前月比では米州と日本が減少

- 自律神経から「頑張りすぎ」を可視化、村田製作所