ARMから見た7nm CMOS時代のCPU設計(13)~高移動度FinFETの期待と現実:福田昭のデバイス通信(24)(2/2 ページ)

ゲルマニウム・トランジスタではリーク電流が増大

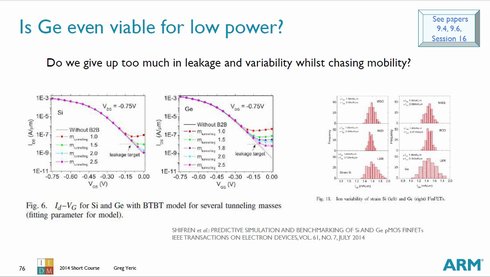

ゲルマニウム(Ge)FETが抱える問題は、他にもある。リーク電流がシリコン(Si)FETに比べると高いことだ。リーク電流の要因の一つであるバンド間トンネリングでは、ゲート電圧が低い領域ではSiよりもGeのリークが大きい。待機時消費電力の制約が厳しいモバイル用CPUでは、Ge FETのリーク電流は無視できない。

トランジスタ間の特性ばらつき(オン電流のばらつき)は、Si FETと比べてGe FETが特に小さいわけではない。むしろ、ばらつきはSi FETよりもGe FETがやや大きい。この点も問題である。

左はトランジスタにおけるドレイン電流とゲート電圧の関係。左がSi FET、右がGe FET。バンド間トンネリングによるリーク電流を比較した。右はオン電流のばらつき。左がSi FET、右がGe FET(クリックで拡大) 出典:ARM

左はトランジスタにおけるドレイン電流とゲート電圧の関係。左がSi FET、右がGe FET。バンド間トンネリングによるリーク電流を比較した。右はオン電流のばらつき。左がSi FET、右がGe FET(クリックで拡大) 出典:ARM低ゲート電圧での解決策としてトンネルFETが浮上

そこで代替策として、従来とは異なる原理でトランジスタ電流をオン・オフするFETの研究が進められている。従来のMOSFETでは、ゲート電圧によるポテンシャルの変化を利用してソースからチャンネルに対して少数キャリア(nチャンネルMOSでは電子)を注入していた。

ポテンシャルの変化を利用したキャリア注入は、ゲート電圧が高いときは非常に上手く働く。しかしゲート電圧が低くなるとポテンシャルの変化がわずかになり、キャリアの注入が減る。すなわち、トランジスタ電流が低下する。

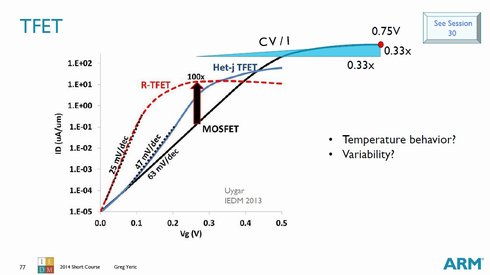

この問題の解決策として浮上したのが、ポテンシャルではなく、トンネル効果を利用してキャリアを注入するトランジスタである。トンネルFET(TFET)と呼ばれている。トンネルFETでは、低いゲート電圧でもドレイン電流が急峻に立ち上がる。

ゲート電圧が0Vから増加するときに、電流の立ち上がりの急峻さは「SS(Subthreshold Swing)」あるいは「S係数」と呼ぶ数値で示すことが多い。具体的には、電流が一桁増えるのに必要なゲート電圧の増加量(mV/dec)である。この値が低いほど、電流が急峻に立ち上がる。

ARMの講演では、従来のMOSFETのSSが63mV/decであるのに対し、トンネルFETのSSは25mV/decと低い。例えば0.25V~0.3Vのゲート電圧で比較すると、トンネルFETのドレイン電流(単位長当たり)は、従来のMOSFETの約100倍にも達する。

(次回に続く)

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

Special Contents

- PR -Special Contents 2

- PR -記事ランキング

- 半導体メーカーの「悲喜こもごも」 絶好調のTSMC、人員削減のST

- IntelがAltera売却へ、株式51%を米投資ファンドに

- 2024年の半導体市場は21%成長 NVIDIAが初の首位に

- ミネベアミツミが芝浦電子買収へ 「8本槍」戦略強化に向け

- 世界半導体市場が10カ月連続で17%以上成長 2月として過去最高に

- 2035年のウエハー需要を予測する ~半導体も「VUCA時代」に

- チップに「水路」を作り冷却液を流し込む 高効率に放熱

- AIのデータ転送問題解決に王手、シリコンフォトニクス新興企業

- 1インチサイズの全固体電池を10秒で作製 レーザーで加工

- トランプ政権の「アメとムチ」 Intelは補助金を受け取れるのか

FinFET以降の半導体製造技術はどう進む? IBMの見解

FinFET以降の半導体製造技術はどう進む? IBMの見解 ムーアの法則、半数以上が「22nm以降では難しい」――半導体業界リーダー調査

ムーアの法則、半数以上が「22nm以降では難しい」――半導体業界リーダー調査 ムーアの法則、その行方を聞く

ムーアの法則、その行方を聞く ムーアの法則は5nmに壁、民生用LSIは28nmで様子見を

ムーアの法則は5nmに壁、民生用LSIは28nmで様子見を ムーアの法則はまだ終わらない、存続の鍵はGaAs材料

ムーアの法則はまだ終わらない、存続の鍵はGaAs材料