究極の低電圧・低消費を目指すスティープスロープFET:福田昭のデバイス通信 IEDM 2015プレビュー(9)(1/2 ページ)

2015年12月8日に開催されるセッション22のテーマは「スティープスロープ・トランジスタ」だ。このトランジスタの実現手法に関する研究成果がIntelなどから発表される。同日夜のパネルディスカッションでは、オンチップの相互接続技術や、CMOS技術が直面している課題について議論が行われる予定だ。

トンネルFETと負性容量FETがスティープスロープの候補

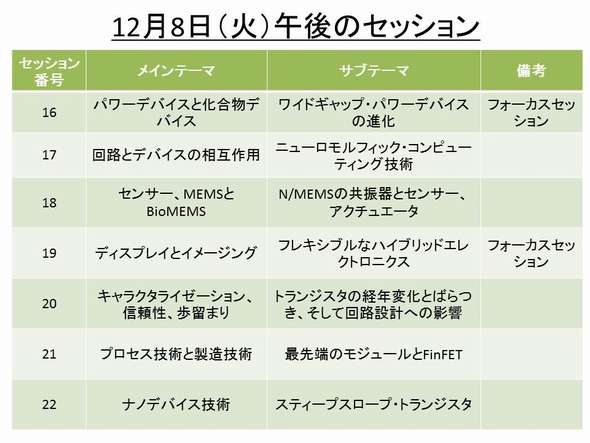

2015年12月に開催予定の国際学会「IEDM 2015」から、カンファレンス2日目である12月8日(火)の午後に予定されている技術講演と、同日の夜に予定されているパネル討論を解説する。8日午後の時間帯では、セッション16からセッション22までの7本のセッションが並行に進む。前回に続いて残りのセッション、すなわちセッション22(ナノデバイス技術)の講演をご紹介しよう。

セッション22(ナノデバイス技術)のサブテーマは、「スティープスロープ・トランジスタ」である。

スティープスロープ・トランジスタは、FETがオフからオンに切り換わる手前の領域(サブスレッショルド領域)で、ゲート電圧の微小な増加に対してドレイン電流を急峻に立ち上がらせることで、低い電源電圧での動作を可能にする。従来構造のFETでは、サブスレッショルド領域における電流の立ち上がり特性は、60mV/dec(電流を1桁増やすためにゲート電圧を60mV上げる必要があるという意味)が限界とされてきた。スティープスロープ・トランジスタでは、この限界を超えることで低い電圧での動作を狙う。

スティープスロープ・トランジスタの代表的な実現手法は、トンネル効果によって電流を流す「トンネルFET」である。このセッションではまずIntelが、トンネルFETの研究状況を招待講演で概観する(講演番号22.1)。n型のトンネルFETとp型のトンネルFETを実現する有力候補は、III-V族化合物半導体を利用したヘテロ接合のトンネルFETである。ファンアウトが4のインバータ論理素子で動作時の消費電力エネルギーを従来のCMOS回路と比較すると、消費エネルギーを従来の半分以下に低減するためには、サブスレッショルド特性(SS)を53mV/decよりも向上させる必要があるとする。

続いてPeking UniversityとSMIC(Semiconductor Manufacturing International Corporation)の共同研究グループが、CMOSベースのシリコンに相補型トンネルFETを作り込むファウンドリ・プラットフォームを報告する(講演番号22.2)。300mmウエハーのバルクCMOSファウンドリ・プロセスに構築する。実際にインバータ論理素子などを試作して性能を評価し、回路特性を改良した。電源電圧が0.4Vと低い条件下で、動作速度を93%向上し、消費電力エネルギーを66%低減できた。

スティープスロープ・トランジスタのもう1つの実現手法は、ゲート絶縁膜を強誘電体に置き換えたFETである。強誘電体膜によってゲートの静電容量が負性容量となり、急峻なサブスレッショルド特性を実現できる。

強誘電体材料の候補は、HfZrOx(ハフニウムジルコニウム酸化物)である。台湾のNational Nano Device Laboratoriesを中心とする共同研究チームは、Hf0.42Zr0.58O2をゲート絶縁膜スタックに採用した負性容量FinFETを試作した(講演番号22.6)。サブスレッショルド特性(SS)は55mV/decであり、まだ改良の余地がある。

Copyright © ITmedia, Inc. All Rights Reserved.